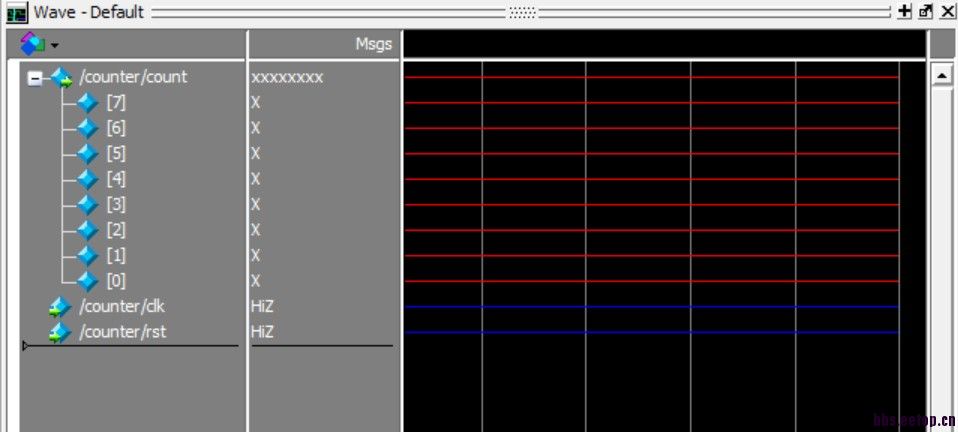

modelsim 仿真时出错

你给激励了么

我的有一次是因为没赋初值,

没有时钟

时钟都是高阻没有值的,应该是时钟问题

非常感谢各位大侠的回复,激励是不是软件自带的还是自己加的,真不好意思 哈 我是初学者

自己写testbench给激励

根本就没有跑啊

非常感谢

您好!为什么对testbench编译后,界面下方怎么出现no design loaded,no context

仿真波形还是出不来,请求回复

您好!为什么对testbench编译后,界面下方怎么出现no design loaded,no context

仿真波形还是出不来,请求回复

我个人意见,你应该是个超级初学者,modelsim的 UG全看一遍再说吧,这样瞎试效率很低的

可能代码有问题,或者编译时加载文件有问题或者其他错误,先保证代码无误,再按modelsim流程操作,有问题可以google,再不行请上传源码包括testbench

個人猜測是 library path 的問題

module cnt10(clk,rst,ena,q,cout);

inout clk,rst,ena;

output [3:0]q;

output cout;

reg [3:0]q;

always @(posedge clk or posedeg rst)

begin

if(rst)q=4'b0000;

else if(ena)

begin

if(q<9)q=q+1;

else q=0;

end

end

assign count=q[3]&q[0];

endmodule

module cnt10_tb;

reg clk,rst,ena;

wire [3:0]q;

wire cout;

cnt10 U1(clk,rst,ena,q,cout);

always #50 clk=~clk;

initial

begin

clk=0;rst=0;ena=1;

#1200 rst=1;

#120 rst=0;

#2000 ena=0;

#200 ena=1;

#2000 $finish;

end

endmodule

请各位大师帮忙弄弄,小弟在这儿先谢过了啊!

这是一本书上的example

时钟没有激励

应该是对信号赋值冲突吧