综合后,比较器的面积开销问题

时间:10-02

整理:3721RD

点击:

最近在思考一个问题

比如

if ( cnt == 9 ) next_state = `DESTINATION;

else cnt++ ;

or

if ( cnt <10 ) cnt++ ;

else next_state = `DESTINATION ;

这两种代码,综合出来的比较器,谁的面积开销大一些?

是a==b的。

是a==b的。

比如

if ( cnt == 9 ) next_state = `DESTINATION;

else cnt++ ;

or

if ( cnt <10 ) cnt++ ;

else next_state = `DESTINATION ;

这两种代码,综合出来的比较器,谁的面积开销大一些?

个人感觉==占用的面积比较少,全凭目测。

实践综合一下,估计一样,综合器会优化的。

求实践后的结论

不会一样,肯定第一种面积小

从代码健壮性的角度,建议第一种写法写成f ( cnt >= 9 ) ,因为要是某种情况下突然变为10了呢?那不就跑死了? 如果改成这样,那就更加完全等价了。

我也觉得第一种。=要比<的逻辑重复少吧

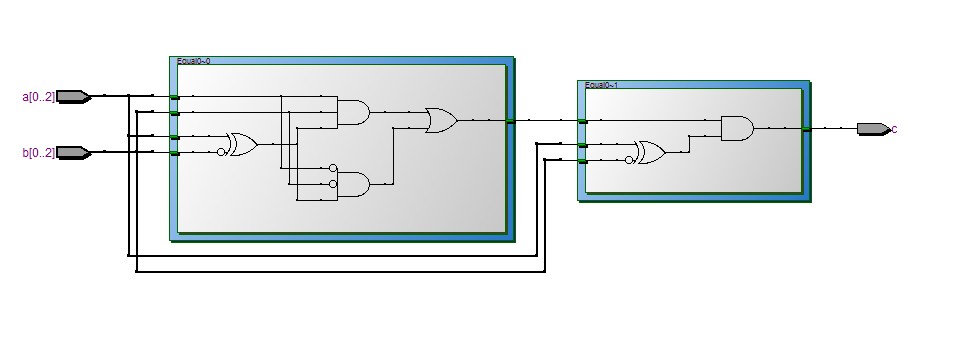

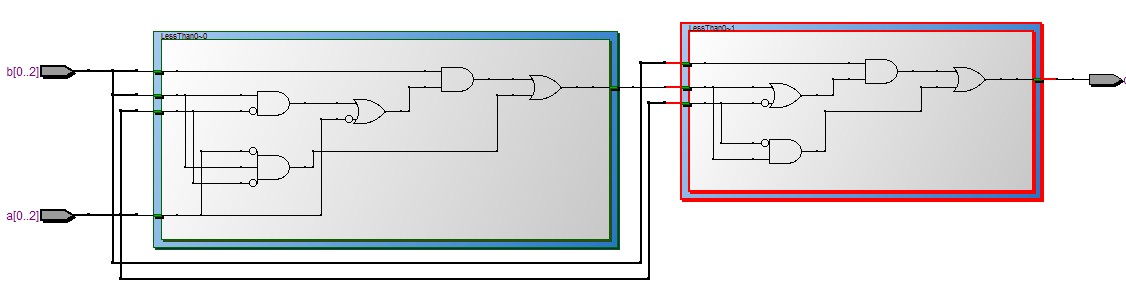

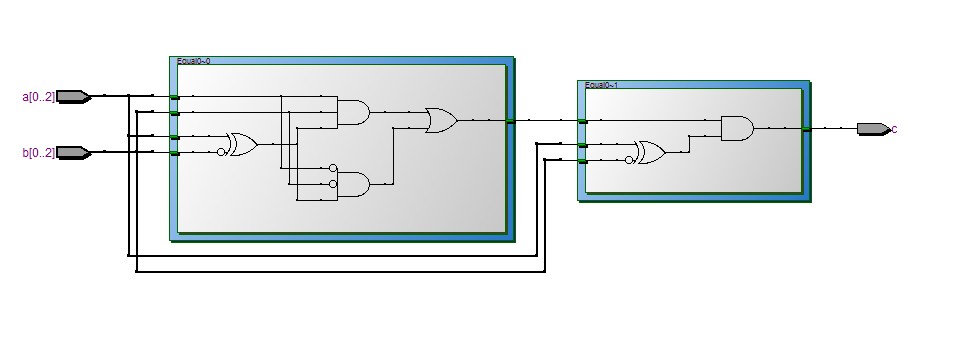

module pinout(input [2:0]a,

input [2:0]b,output c);

assign c=(a<b);//or assign c=(a==b);

endmodule在quartus ii中试了一下

是a==b的。

是a==b的。

我倾向于认为a==b的时候少,毕竟现在STDcell里面单独的异或门!

同觉得第一个简洁,latch前的comb感觉第一个要简单一点