问一个跨时钟域同步的问题

时间:10-02

整理:3721RD

点击:

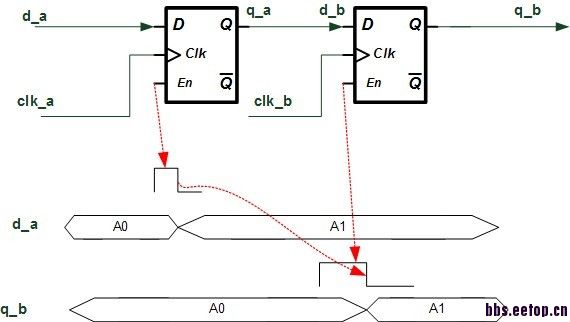

如图,clk_a和clk_b两个时钟不相关。clk_a Domain有个pulse信号,同时更新q_a (从A0变为A1)。这个pulse信号经过一个pulse转换器会在clk_b Domain产生同样的一个cycle的pulse信号。

clk_b Domain会根据这个新的pulse信号区去捕获q_a的值,随即更新q_b(从A0变为A1)。

现在问题来了,虽然这两个pulse之间的时间差至少是两个clk_b cycle。但q_a到d_b的delay如何保证?因为clk_a和clk_b是false path.

如果q_a到d_b路径太长,这套逻辑就乱了。

这套逻辑和握手信号同步本质上是一样的。

后端工具能保证任意路径都不要太长么?design rule check能派上用场么?

求解答。

先说说你的最终目的是什么,如果只是把clk_a时钟域的d_q传送到clk_b时钟域的q_b,那直接DFF打两拍就可以了。

嗯,单比特确实如此。

如果是多比特信号的同步呢?有人说可以用FIFO,未免有点小题大做。而且深度为1的FIFO本质上也是握手同步,ptr的逻辑和data path本是是分开的,如何保证data path的delay不会太长?

如果你的d_a是多比特信号,而且en信号可能连续有效,那么只能用异步FIFO。其他的方式做不到。(至少我想不到别的简单方式,呼唤高手指点。)而且你的en那边还得加一个FIFO满标志的握手信号,不然FIFO可能溢出。除非你的源端保证数据流没那么快。

q_a到d_b, 这个一般没有人管,当然这个是不严谨的。(但是P&R tool的算法一般也不会让这两个寄存器隔太远,因为P&R tool都是尽力做到最好的,会努力把相关的逻辑放在一起。)所以一般都假设这个wire delay不会超过2T clcok_B的周期。

如果小编实在不放心,DC/PT 有个"set_max_delay"的constraint,但是这个指令在算delay的时候跟clk_A / clk_B的波形(rising edge的时间差)有关系,你可以尝试下。