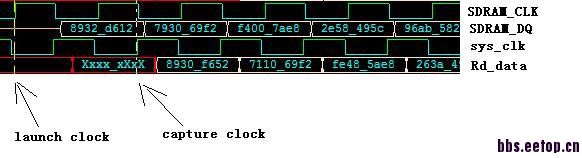

SDRAM控制器后仿真遇到问题,如图所示,求指点

因为从仿真结果看来,SDRAM_DQ相对于sys_clk来说,数据保持时间偏小,因此我暂时用的是在时序约束中增加输入端口延迟的方法,以增大SDRAM_DQ相对于sys_clk的数据保持时间,但是我猜测这种方法不可靠,请问大家有没有更好的办法?在实际工程中大家是怎么处理的?

(目前我设置的时钟频率为100MHz,时钟有效沿都是上升沿)

固定一个时钟,然后一点点调整另一个时钟相位,总能找到安全窗口,否则你需要从理论上向下计算出这个安全窗口。

我也在搞sdram,用的是lattice的模板做的工程!读写有问题,写的时候不管对最低的二根地址线那个空间写,都会更改这四个空间的值,而且读一块我没操作的地址(8个促发),DQ最多只有四个值(值是随机的没有规律),如果读我写过的地址,DQ输出全是我的写的值!感觉读写都有问题!现在不知道如何去调试!

fpga的话结合逻辑分析仪随便调

如果是用的altera的片子,建议用signaltap抓一下,看看时序,当然首先确认硬件上有无短路。

嗯,昨天我试试对初始化进行了处理,使其上电后进行二次初始化,我遇到的问题解决了,可能是对sdram的初始化没有完成造成以上原因的!白费我调时序,刷新那么多天!多谢了!

您好? 请问您有没有用过3Dplus公司的ddr啊?

您好!请问,您对3D plus ddr有了解吗?该公司的3D1D2G32芯片是有两个MT46V6416XX_75ddr颗粒,封装而成的。因此,该芯片的位宽可看做32bit,芯片的ck和ck_n管脚只有一组。我现在想用的数据位宽为32bit,所以需要2个MT46V6416XX_75,即1片3D1D2G32芯片。在MIG核设置后,生成的ucf中,ck和ck_n有2组,dqs为4bit。而现在只有1组ck和ck_n管脚和2bit的dqs。我该如何使用该芯片。由于刚开始学ddr,对其不太熟悉,望不吝赐教!

不好意思,没有用过!但是根据你的描述,既然人家做到了二合一,是不是控制信号也做到了二合一了,仔细看看手册应该能找到答案的。