Cyclone4时钟树的疑问?

时间:10-02

整理:3721RD

点击:

Cyclone4时钟树C6等级的可以500MHz,

2013/8/16 14:50:12

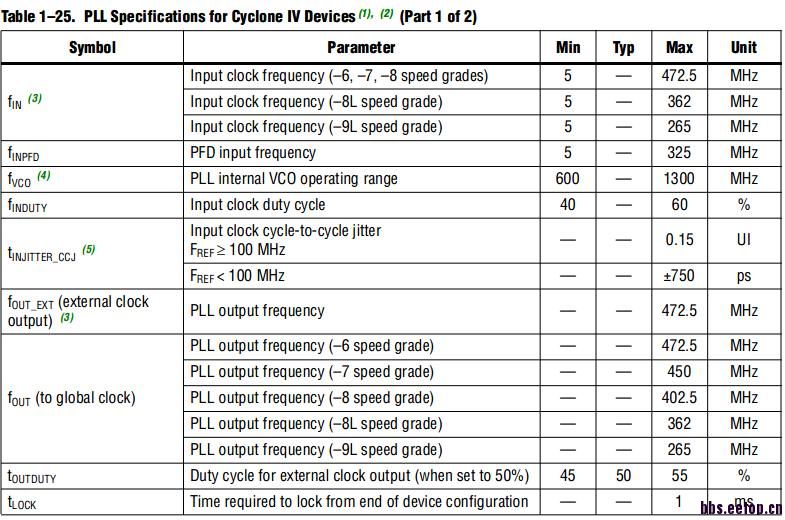

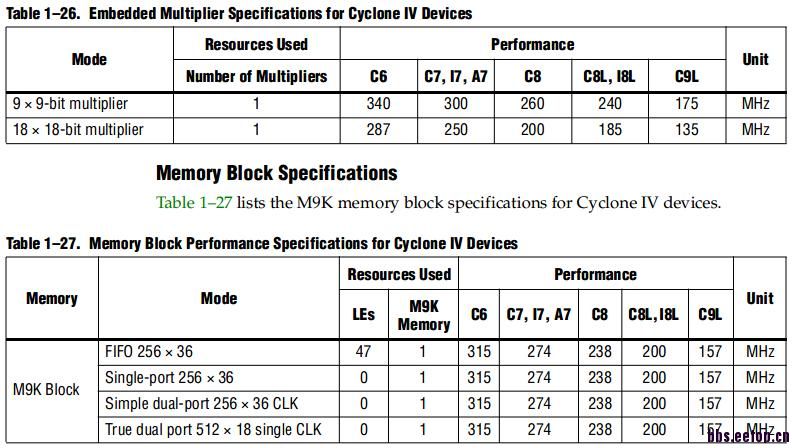

可是它里面的pll,ram,dsp等模块。没有达到500MHz的

那么他的这个500MHz究竟体现在哪里?

什么地方能用到这个500MHz?

跑端口的

引脚输出?还是什么?

弄个寄存器输出接个反门再送回寄存器的输入,用1个LE即可实现,这个电路的速度可以到500MHz了吧

问题是500M的时钟怎么来?PLL都出不来

VCO 最高可以到1300MHz。给PLL输100MHz, multiplier设5, divider设1, 就可以生成500MHz的

Clock Networks and PLLs in Cyclone IV Devices, 5-26:

按照手册的数据,确实没有办法使电路跑在500MHz,因为PLL出不来,I/O也翻转不过来。不过这一项本身只是说时钟网络的性能最差也可以达到500MHz(可以翻转),而实际上能跑的频率肯定比手册上的最差值要高。假如你发现实际上PLL可以稳定输出500MHz,或者你发现可以从I/O灌进一个SAW振荡器输出的500MHz时钟,那你可以毫不担心时钟网络会成为瓶颈。

学习一下!

好像到不了500DE