关于乘法器的问题

时间:10-02

整理:3721RD

点击:

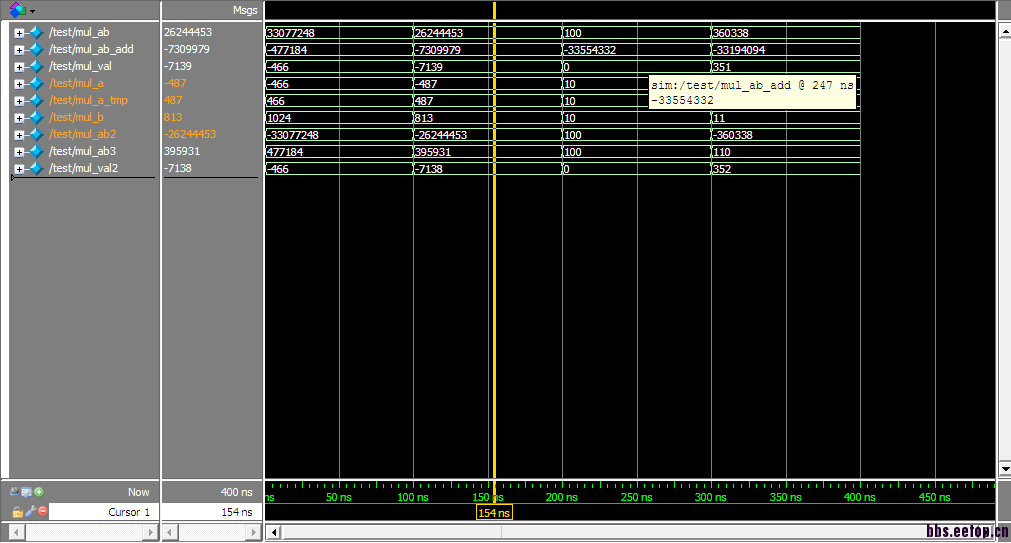

在verilog仿真中,乘法器是如何识别有符号/无符号数的.请看以下仿真结果:

如何解释比较合理?

1)所有变量已经都声明为reg,wire形,没有定义为有符号数,但mul_ab3和mul_ab2的值不一样

2)当mul_a为”负数“时,乘法器计算mul_ab2的算法貌似是,mul_a的值*mul_b外加两个符号位?

为啥乘法器左边使用选择逻辑之后结果就变了呢?

请高人指点。

module test;

reg [14:0] mul_a;

reg [11:0] mul_b;

wire [26:0] mul_ab,mul_ab_add;

wire [14:0] mul_val;

wire [26:0] mul_ab2,mul_ab3;

wire [14:0] mul_val2;

wire [14:0] mul_a_tmp;

initial begin

mul_a = -15'd466;

mul_b = 12'd1024;

#100;

mul_a = -15'd487;

mul_b = 12'd813;

#100;

mul_a = 15'd10;

mul_b = 12'd10;

#100;

mul_a = -15'd10;

mul_b = 12'd11;

$stop;

end

assign mul_ab = mul_a * mul_b;

assign mul_val = mul_ab[24:10];

assign mul_ab_add = {~mul_ab[26:25],mul_ab[24:0]};

assign mul_a_tmp = (mul_a[14] ? (~mul_a + 1) : mul_a);

assign mul_ab3 = mul_a_tmp * mul_b;

assign mul_ab2 = (mul_a[14] ? (~mul_a + 1) : mul_a)*mul_b;

assign mul_val2 = (mul_a[14] ? (~mul_ab2[24:10] + 1) : mul_ab2[24:10]);

endmodule

默认是当做无符号数来处理的

学习一下。

verilog 2001 加入了singed 的定义

比如

module multiplier (

parameter SIZE = 8;

output reg signed [SIZE-1:0] F;

input [SIZE-1:0] A,B);

~

endmodule

reg ,wire型都是无符号数,integer型的是有符号数