请教大家一个异步复位的问题

请教大家一个异步复位的问题:

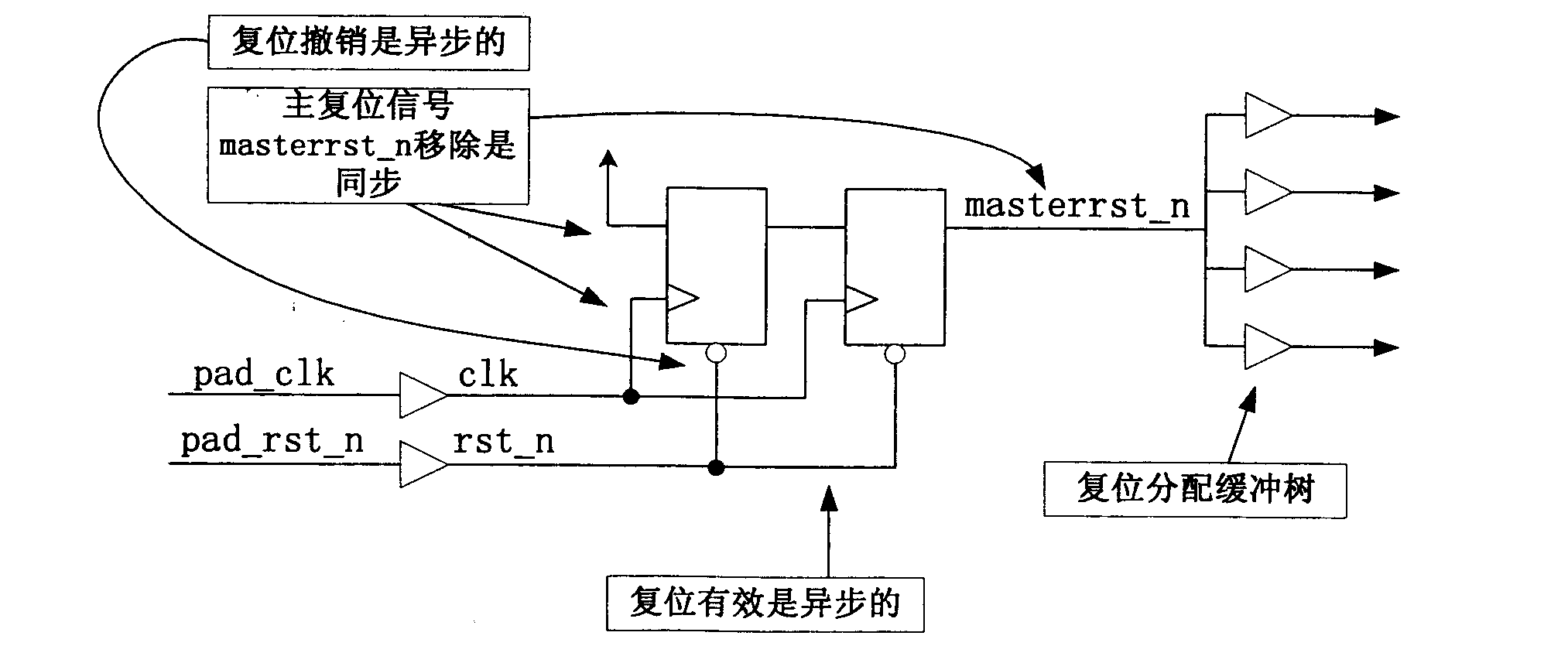

目前我们用的异步复位同步释放,都是用如图中所示的方法,用两级触发器同步异步复位信号,我在一篇论文中看到说用两级触发器发生亚稳态的概率比一级触发器的要小很多,大概是一级触发器发生亚稳态概率的平方。我觉得这样计算概率不太对,对于第二个触发器而言,它复位时发生亚稳态的概率并不受第一级触发器的影响。

我的理解是:其实就概率而言一级触发器和两级触发器是一样的,两级触发器比一级触发器的好处就是使同步后的复位信号至少保持1个cycle的时间。

希望各位大侠指正!

自己顶一下,希望有大侠来解决

如果每个寄存器发生亚稳态的概率都是X的话,

第一级的X乘以第二级也是X,那么一共的概率就等于X*X ,可不是X的平方吗?

谢谢三楼的大虾的答复,我的疑问并没有消除,希望更深一步的分析,希望更多大虾一起讨论。

我们单纯的看第二个寄存器,它的Reset信号和它的clk关系是不受第一级寄存器的影响的,所以说它发生亚稳态的概率是不变的,假设为X。第一级寄存器发生亚稳态的概率也为X,所以这两个寄存器发生亚稳态的概率应该大于大于等于2X,而非X的平方。

1.亚稳态是在setup/hold时间不满足的时候出现的

2.亚稳态是否存在与reset的解除时间没有关系,但reset可以屏蔽亚稳态;如果reset解除时setup/hold时间不满足,还是会出现亚稳态,反之就不会出现亚稳态。

3.亚稳态出现后,会有一个振荡期,在振荡结束后,亚稳态会恢复到0或者1的固定值上,从而结束亚稳态。

4.根据不同的工艺这个振荡期的时间长度不同,通常在ps或ns级别,通常小于1个clk时间(除非你的频率非常高)

5.组合逻辑会大大增加这个振荡期的时间长度【关键点】。

因此

1.数据穿越异步时钟,一定会周期性地出现亚稳态,因为时钟跳变时数据也可能会跳变

2.通常亚稳态出现后,在一个clk周期内会结束振荡,要保证结果是0或是1都不会出错,因为下一clk会采对数据

3.禁止让亚稳态传递到组合逻辑上,否则无法预知振荡期是否会超过一个clk,如果超过,则组合逻辑后段的FF也采到亚稳态,再经过后面的组合逻辑继续振荡,就会出现亚稳态的传播,系统宕掉的机率很高

所以,有可能出现亚稳态的FF后不插任何组合逻辑,直接跟一个FF,可以有效阻止亚稳态传播。

至于概率,如果能在一个clk下稳定,就是0,否则就是100%。

LZ图里的复位,上拉成了'1',复位线上本来就不会有亚稳态的,应是保证reset大于一个clk。

这是概率上的问题了,如果A,那有B的概率为X;如果B,那C的概率为X; 如果A导致B事件发生并且也导致C发生的概率是相乘而不是相加,

类似于A走到中点B有2种可能,B到C有3种可能,那A到C呢?6种可能,而不是5种,

不明白啊

我也有一些疑问,就是当rst释放刚好跟clk的上升沿赶到一起时,无论是不是两级DFF,后一个DFF处都会产生recovery/removal的问题,这个也会影响后一个DFF的输出吧。

个人认为rst的上升沿最好先用clk sync一下,再给到图中两个DFF的rst端(这样的话一个就够了吧,之前用两个的作用不太清楚),以保证recovery/removal满足 。

是不是有这个必要,那位大虾给解释一下啊!

jacky.sun 想法是正確的

针对单个寄存器而言,后一级的概率与前一级应该一样是X,只是前一级可以采一拍(无论对错)使之是一个稳定电平,保证后一级采对一个正确的电平

当然针对整个设计而言,多一级寄存器使得信号经过该电路以后出现亚稳态的概率确实应该是X*X

对小编的想法不敢苟同

reset线上是有可能出现亚稳态的

就是像楼上某同学说的 recovery的问题 只要reset的失效沿距下一个时钟的有效沿过近(recovery time之内)

就有可能出现亚稳态 具体请参考带clear端的dff的原理结构图

而概率的问题 期待其他同学解答