如何用HDL实现2.5分频,且占空比是50%呢?

时间:10-02

整理:3721RD

点击:

如题如题!

先4倍频,再10分频

恩,是一种办法,

怎样用HDL描述呢?

占空比是PR实现的

数字做4倍频还是有点难度的吧?

调用dcm的vhdl就行了

此话怎讲?PR不是只会影响skew啊

你要表达是的奇数分频还是小数分频啊?

2.5分频,且50%占空比

使用上下沿,可以做到50%占空比吗?

能给说一下怎么做吗

我也觉得这个问题不好弄,所以才来看看大家的建议喽...

如果你只拿来只是做仿真的话, 就用时钟上下沿计数器来做,如果需要综合的话, 那就去看看小数分频怎么做的

使用两根wire 来复制clock,通过约束使两根wire 延迟相差四分之一个clock,然后异或一下可以产生一个4倍频。

我也正要学习这一块,谁有比较专业的资料呢

整数倍频不难,X.5倍也不难,难的是后者的占空比为50%

这是模电操作吧!求详细,此问题严重关注中

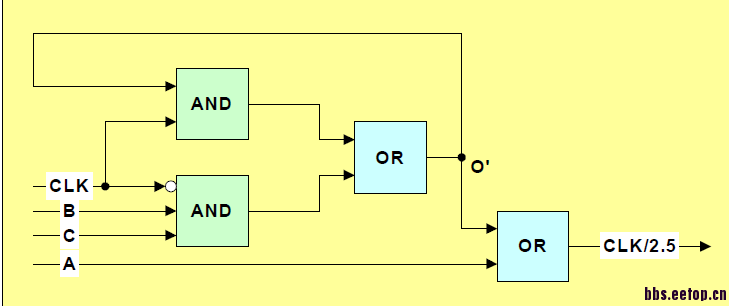

LZ,这个应该能在硬件层面实现2.5分频,但是输出必须按照上面前辈所说的适当处理下,可以得到你想要的结果。