关于实际modelsim仿真中,引脚信号与内部信号不相同的问题

时间:10-02

整理:3721RD

点击:

这几天遇到一个问题,百思不得其解,借问一下论坛的各位。

如下面代码所写的,其中有一句:

assign {sdram_cke, sdram_cs_n, sdram_ras_n, sdram_cas_n, sdram_we_n} = sdram_cmd_r;

在我的理解是,sdram_cke等同于sdram_cmd_r[4],sdram_cs_n等同于sdram_cmd_r[3],如此类推

其中sdram_cke,sdram_cs_n为外部输出端口引脚,sdram_cmd_r[4]和sdram_cmd_r[3]为例化模块的内部信号。

个人觉得两个信号应该是一样的,但是用modelsim仿真两个信号却是不相同的。

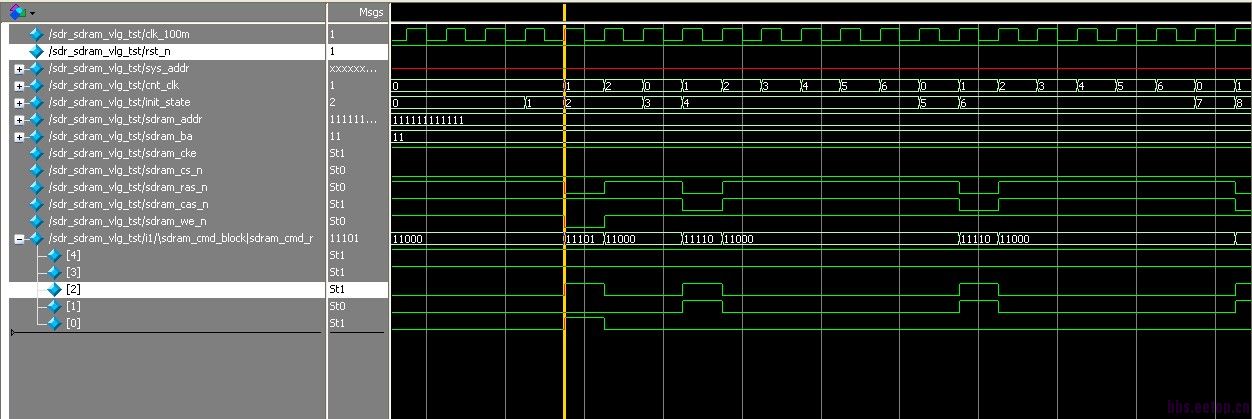

见下图所示:

如图所示,黄线处sdram_cke, sdram_cs_n, sdram_ras_n, sdram_cas_n, sdram_we_n这五个信号都正确,分别是10010(此时为`I_PRE)状态,但是sdram_cmd_r信号却是11101,明显不相等。求助一下各位,到底是什么回事呢?

自顶,求各位指点迷津

应该是multidrive 的问题吧,sdram_cke,sdram_cs_n 还接了其他的地方吧,作为新手我也遇到过。

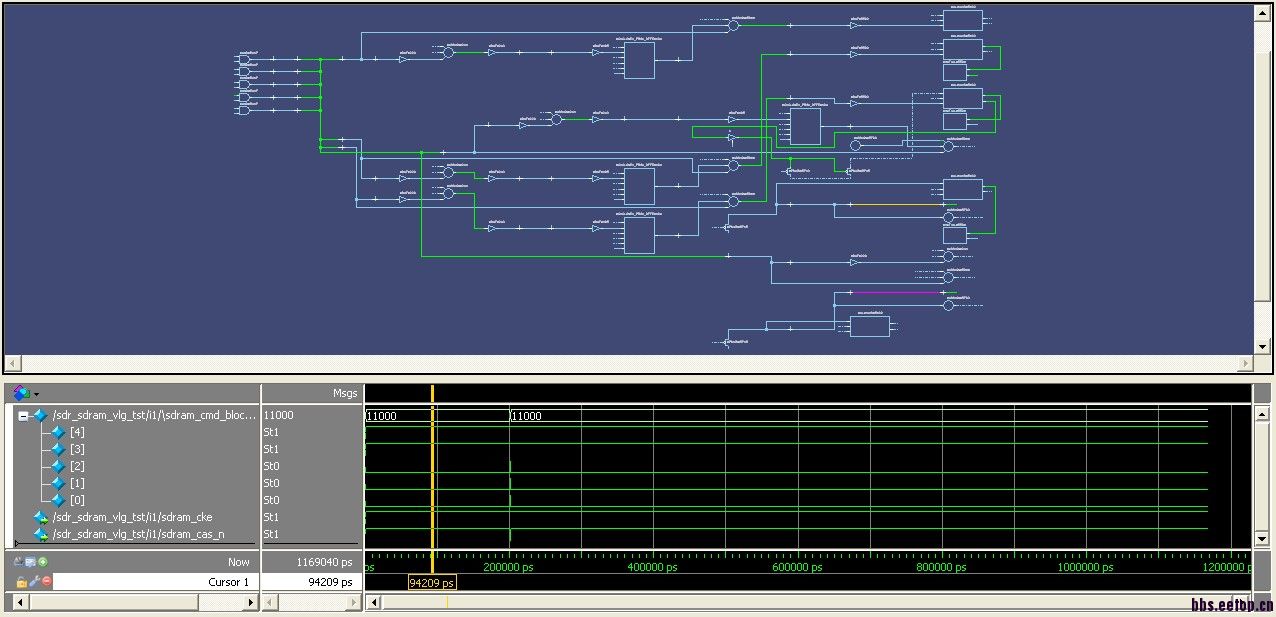

应该不是,今天我用multisim的数据流视图看了一下。

sdram_cmd和上面几个信号不是连在一起的,也就是这几个信号不是等同的。

应该是加了assign语句的关系,sdram_cmd后面加了几个buffer?

可以看下面的图:

其中绿色的是sdram_cmd的一位信号,红色和黄色分别是sdram_cke和sdram_ras信号。

很明显不是连在一起的。不知道这个解释是否正确。

我只是初学者

我看一楼图里面的相应位的数都是反的,除了最高位

我怎么看的像有符号数的反码呢

一定要用{}吗,分别进行赋值会不会没这个问题呢?