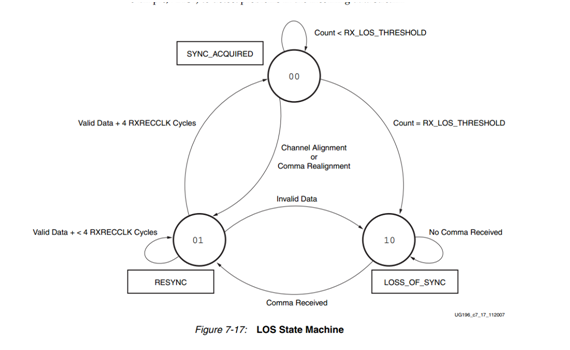

V5系列中GTP_DUAL的同步状态机

这是V5系列的GTP_DUAL中同步状态机的跳转图,UG196.pdf的P162。

关于这个图,我有几个疑惑

首先是左边的两个条件:Valid Data + 4 RXRECCLK Cycles 和 Valid Data + < 4 RXRECCLK Cycles看不懂是啥意思,下面也没有文字说明,那位大X帮忙解答一下。

另外,按照我的理解状态机在SYNC_ACQUIRED时才算作同步了,但是实际测试时,发现状态机始终处于RESYNC的状态,用RESYNC作为同步上的状态,项目也能正常运行。

请问BBS里面的各位大X,这个正常吗?还是说GTP_DUAL正常运行的时候同步状态机一直处于RESYNC状态啊....

Valid Data + 4 RXRECCLK Cycles可能表示连续检测到4个有效数据。

至于状态停留在RESYNC状态,这肯定不正常。你项目只是表面看起来跑起来了,底层链路还有问题

我刚刚又做了一下仿真,用CORE_GEN生成的例子,同步状态机也是停留在RESYNC状态。但是这个仿真没能一下就跑起来,还修改了例子中的一些东西。

你确定同步状态机最后会停留在SYNC_ACQUIRED吗? 我在板子上测试的接收数据都是对的,而且中间也没有出现过rxnotintable,rxdisperr,rxbyterealign这些类似的告警,同步状态一直停留在RESYNC上。

按照图中的同步状态机,如果是在RESYNC上的话,只要检测到4个有效数据就能进入SYNC_ACQUIRED,我在RESYNC上停留了很久,而且接收数据也都是对的,肯定能连续检测到4个有效数据的啊,但是就没有再进入SYNC_ACQUIRED状态了

GTP_DUAL的同步状态停留在RESYNC这种情况确实存在,是GTP_DUAL本身存在的问题。XILINX的官网上给出了解决办法,http://china.xilinx.com/support/answers/29218.htm。而且在多通道使用通道绑定时,这个问题是没法解决的。

你是怎么看的状态机,可以看看状态机有没有被优化成ONE-HOT。这个IP我没用过,你再仿真看看。你要不放心可以不用这个同步状态机,自己判断

V5的GTP_DUAL中的LOS State Machine确实存在这个问题,我在XILINX的官网上找到答案了。

单通道时,需要特别设置CHAN_BOND*中的两个值。

多通道时,这个问题没法解决,就只能像你刚刚说的那样,自己做LOS状态机判断了。

具体的解决办法:http://china.xilinx.com/support/answers/29218.htm

修改参数之后,状态机运行就正常了。这个我在仿真和板子上都试过了....