时序分析问题,求帮忙,求指导~~~

时间:10-02

整理:3721RD

点击:

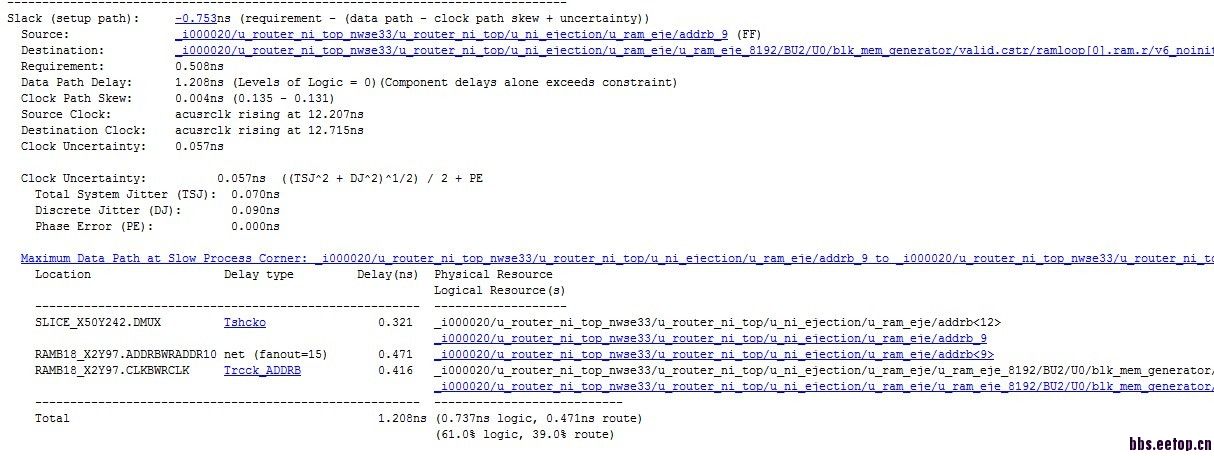

[attach]535795[/attach] 如图所示,显示了我的双口RAM地址到RAM内部的时序达不到要求,其中data path delay后有一句话Component delays alone exceeds constraint ,这是不是说这个ip核跑不到那么高的时钟频率(245.76M)。如果是这种情况,那么解决方法只有降低频率么?请各位高手帮忙看一下,求指导!ps:下板测试的时候功能都很正常,这又是怎么一回事呢?

好像图没有发上来 再来一次

好像图没有发上来 再来一次

为什么requirement 才0.5多一些,异步还是设置时钟频率设置错的?

我也不清楚这里为什么是0.5,我的双口ram A端口进入的时钟频率为78,6432M,而B端口(就是显示有时序问题这个端口)的时钟是245.76M。请问一下您有什么解决办法么?

fpga上跑2GHz的速度,开玩笑呢吧

A口和B口的时钟,是否要设置一个false path,再做时序分析?

requirement 0.508ns

这个是有问题的吧?怎么来的?

学习一下

约束怎么设的,怎么会有requirement 0.508ns。

频率跑不到很高,但是可以扩大位宽来获得大速率。你的问题描述的不是很明白。