spartan6 MCB时序仿真求助

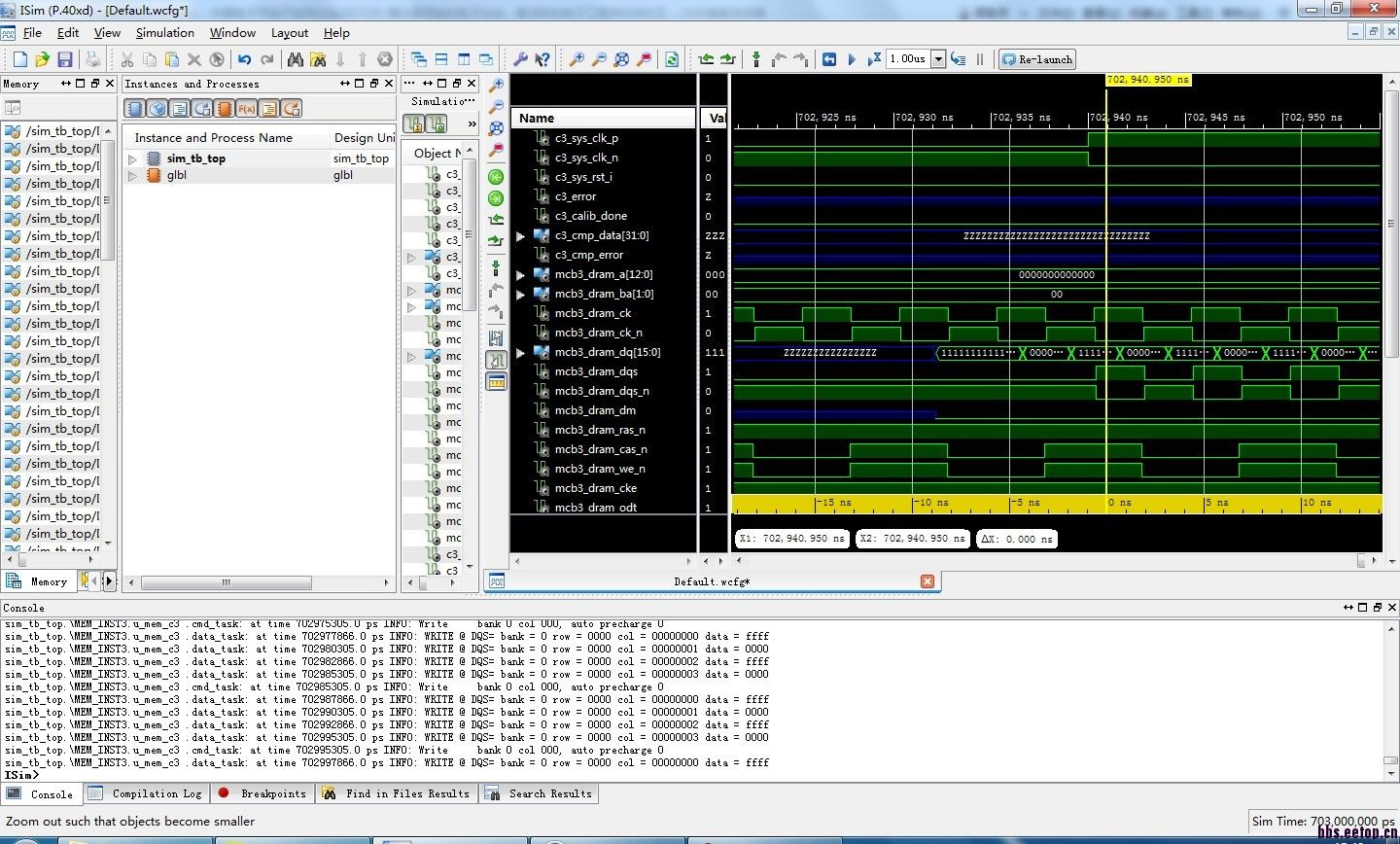

但是进行时序仿真时,碰见一个问题,DQS和UDQS信号不对,前两个数据是写不进去DDR2的,仿真错误信息如下:

sim_tb_top.\MEM_INST3.u_mem_c3 .data_task: at time 702937866.0 ps ERROR: DQS bit 0 latching edge required during the preceding clock period

sim_tb_top.\MEM_INST3.u_mem_c3 .data_task: at time 702937866.0 ps ERROR: DQS bit 1 latching edge required during the preceding clock period

sim_tb_top.\MEM_INST3.u_mem_c3 .data_task: at time 702937866.0 ps ERROR: DQS_N bit 0 latching edge required during the preceding clock period

sim_tb_top.\MEM_INST3.u_mem_c3 .data_task: at time 702937866.0 ps ERROR: DQS_N bit 1 latching edge required during the preceding clock period

sim_tb_top.\MEM_INST3.u_mem_c3 .data_task: at time 702937866.0 ps INFO: WRITE @ DQS= bank = 0 row = 0000 col = 00000000 data = xxxx

sim_tb_top.\MEM_INST3.u_mem_c3 .data_task: at time 702940305.0 ps ERROR: DQS bit 0 latching edge required during the preceding clock period.

sim_tb_top.\MEM_INST3.u_mem_c3 .data_task: at time 702940305.0 ps ERROR: DQS bit 1 latching edge required during the preceding clock period.

sim_tb_top.\MEM_INST3.u_mem_c3 .data_task: at time 702940305.0 ps ERROR: DQS_N bit 0 latching edge required during the preceding clock period.

sim_tb_top.\MEM_INST3.u_mem_c3 .data_task: at time 702940305.0 ps ERROR: DQS_N bit 1 latching edge required

during the preceding clock period.

断开对P2 P3端口的多有操作信号,还是出现这个情况,迷茫了,DQS和UDQS应该是硬核产生的信号,我还能怎样去控制呢?

这个就是时序仿真截图,很明显DQS少了一个周期,不知为何