verilog可以这么写?

时间:10-02

整理:3721RD

点击:

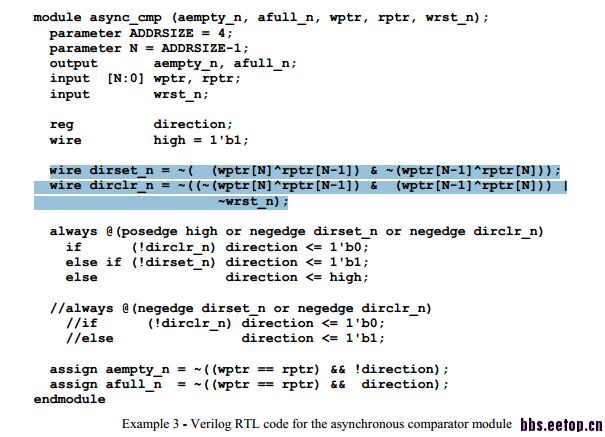

最近在看fifo的相关论文的时候,牛人Clifford E. Cummings(不知道自己google)写了篇相关的fifo论文,写的非常好,但是看到code源代码我有点凌乱了,这是个小白问题。

我们都知道对于wire 输出信号, 只能用assign赋值。

比如说,

Wire c;

assign c = a & b;

怎么论文里直接

wire c = a & b;

这是verilog 2001 enhancement还是我火星了?

论文参考可以看我给的传送门,http://www.sunburst-design.com/papers/CummingsSNUG2002SJ_FIFO2.pdf

该程序出处是Page 9,。

wire c = a&b;

这没有问题!

就像C语言:

int a;

a = 0;

也可以:

int a = 0;

语法支持、编译器支持就行了, 没那么严重!

可以的

谢谢了,楼上的两位兄弟!

谢谢了,楼上的两位兄弟

可以的

可以是可以,我个人还是建议先声明一下,分开写比较清楚,一家之言,呵呵.

这样也可以啊,学习了

学习了,真方便

可以的啊,这好像叫隐似连续幅值

可以的

Verilog语法手册里讲到了,可以的。我们公司写的代码经常这么做

我也是第一次看到verilog的这种写法。受教了

可以的,最近还写了个这种语法 前仿综合都没问题

可以的,最近还写了个这种语法 前仿综合都没问题

第一次见这种写法,受教!

可以,不过我还是不习惯这么写

高深啊,竟然还可以这么写

呵呵,开眼界了

很负责任的告诉你,这样写木有任何问题。ARM 就有这种写法

直接这么用的,没多想过

学习了。之前好像在书上看到过

还是先声明一下吧。传统一点好,语法没必要太花哨。

这样写很常见的