vhdl 求大神指点

时间:10-02

整理:3721RD

点击:

代码如下

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

LIBRARY WORK;

ENTITY TEST IS

PORT (

CLK : IN std_logic;

d : out std_logic_vector(3 downto 0));

END TEST;

ARCHITECTURE SIM OF TEST IS

FUNCTION TMR (A,B,C:STd_LOGIC_VECTOR( 3 DOWNTO 0)) -- 三路表决器函数

RETURN STD_LOGIC_VECTOR IS

variable RESULT : STD_LOGIC_VECTOR(3 DOWNTO 0);

begin

for i in 3 to 0 loop

RESULT(i) := ((A(i) AND B(i)) OR (C(i) AND B(i)) OR (A(i) AND C(i))) ;

END LOOP;

RETURN RESULT;

END FUNCTION TMR;

SIGNAL A :STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL B :STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL C :STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

P_RUN ROCESS(CLK)

BEGIN

IF CLK='1' THEN

A<="1101";

B<="1111";

C<="1111";

D<= TMR(A,B,C);---A,B,C调用函数表决

ELSE

A<="0000";

B<="1000";

C<="0000";

D<= TMR(A,B,C);

END IF;

END PROCESS P_RUN;

END SIM;

tb文件给一个时钟信号

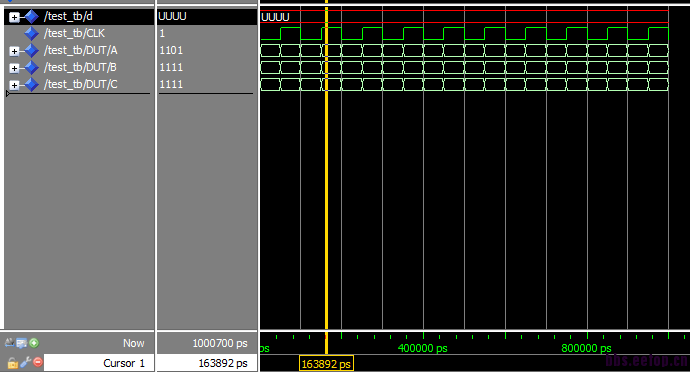

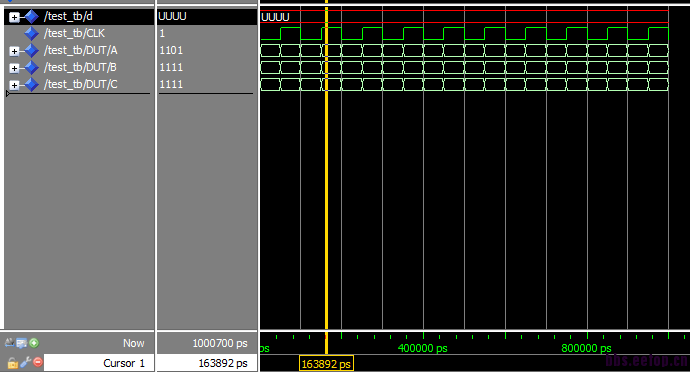

仿真结果如下:三路表决结果出错,未初始化态。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

LIBRARY WORK;

ENTITY TEST IS

PORT (

CLK : IN std_logic;

d : out std_logic_vector(3 downto 0));

END TEST;

ARCHITECTURE SIM OF TEST IS

FUNCTION TMR (A,B,C:STd_LOGIC_VECTOR( 3 DOWNTO 0)) -- 三路表决器函数

RETURN STD_LOGIC_VECTOR IS

variable RESULT : STD_LOGIC_VECTOR(3 DOWNTO 0);

begin

for i in 3 to 0 loop

RESULT(i) := ((A(i) AND B(i)) OR (C(i) AND B(i)) OR (A(i) AND C(i))) ;

END LOOP;

RETURN RESULT;

END FUNCTION TMR;

SIGNAL A :STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL B :STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL C :STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

P_RUN ROCESS(CLK)

BEGIN

IF CLK='1' THEN

A<="1101";

B<="1111";

C<="1111";

D<= TMR(A,B,C);---A,B,C调用函数表决

ELSE

A<="0000";

B<="1000";

C<="0000";

D<= TMR(A,B,C);

END IF;

END PROCESS P_RUN;

END SIM;

tb文件给一个时钟信号

仿真结果如下:三路表决结果出错,未初始化态。

初始态

函数赋值无效怎么搞

莫沉,顶起

你或者改成用复位来实现初始化,或者

SIGNAL A :STD_LOGIC_VECTOR(3 DOWNTO 0) := 0

好像是这样的,你多尝试几遍