ISE中什么是hold path啊?

时间:10-02

整理:3721RD

点击:

ISE中的时序分析器中的路径我只看到两种类型啊。一种是setup path,还有一种是hold path,不是一共有四种类型的路径吗?(Clock to Setup,Clock to Pad,Pad to Pad,Pad to Setup),setup path好像是一般的clock-to-setup路径,hold path是什么呢?

setup和hold啊!建立时间和保持时间的路径

可以看看时序报告的detail部分,其实里面有hold path的定义了

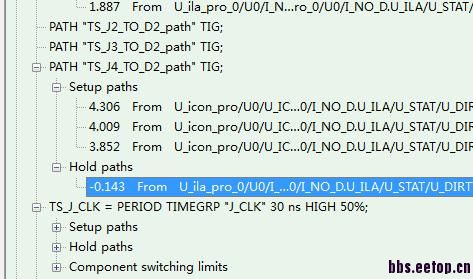

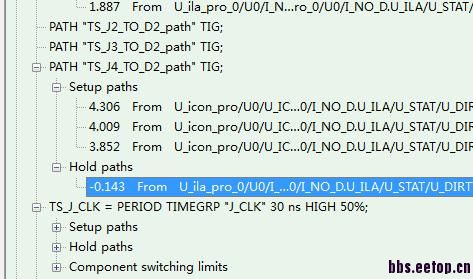

截一段别人的lz参考一下

Slack (hold path): 0.028ns (requirement - (clock path + clock arrival + uncertainty - data path))

Source: RXDATA<14> (PAD)

Destination: rRXDATA_14 (FF)

Destination Clock: clk250m rising at -1.000ns

Requirement: 9.000ns

Data Path Delay: 0.906ns (Levels of Logic = 1)

Clock Path Delay: 10.680ns (Levels of Logic = 4)

Clock Uncertainty: 0.198ns

“Slack (hold path): ”这句就是hold path的定义

另lz混淆了一些概念

时序分析中会分析路径延时,setup/hold time只是路径延时的一种,而setup/hold path则是

组成 setup/hold time的具体路径

供参考!