Cyclone IV设计RGMII接口

时间:10-02

整理:3721RD

点击:

最近用Cyclone IV EP4CE10设计2个RGMII接口,ALTERA参考设计使用RGMII的随路125MHz时钟经过PLL后同步到内部FPGA,但是这样2个RGMII就需要2个PLL,把EP4CE10的PLL用光了,不知各位还有没有其他的设计方法?(主要是将RGMII时钟域转换到内部125MHz时钟域,尽量不使用宝贵的BRAM资源)。

直接用RGMII的随路啊,本来采样数据就要用啊,画蛇添足啊

意思是直接用随路时钟作为FPGA内部时钟?

只要逻辑不是很大的话应该是可以的吧

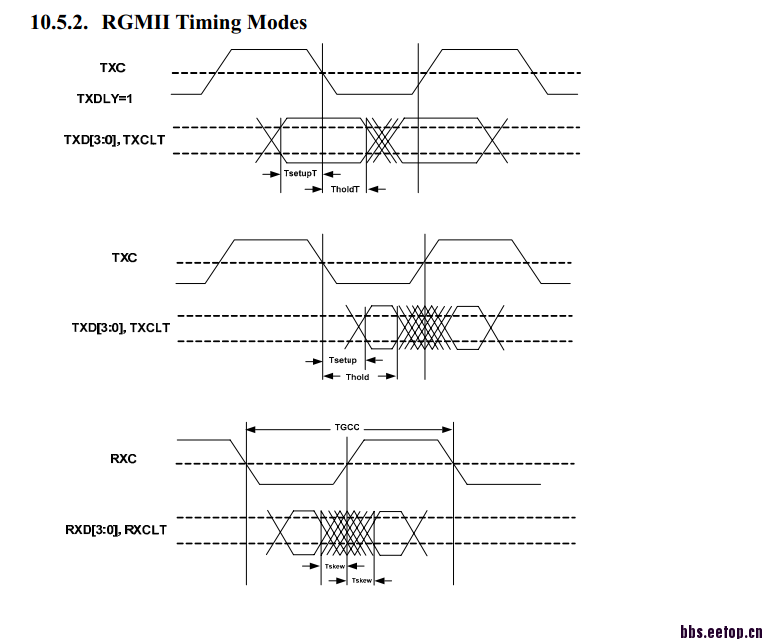

这个rgmII timing mode 不理解,看不懂啊!能否指点一下