求高手帮我看看这个结构在fpga里边有什么好的办法实现

算法可用下面的伪代码表示

u=0.7

for i=1:N

temp=k(i)-u

r(i)=round(temp)

u=r(i)-temp

end

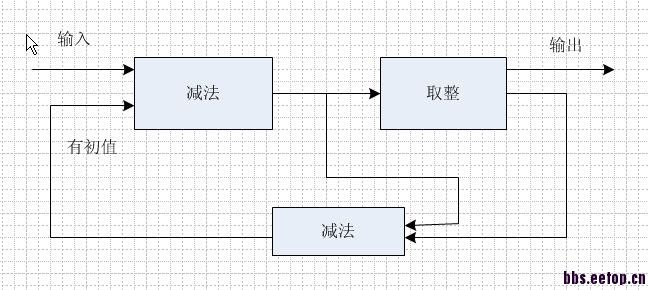

上面k(i)是输入信号 r(i)为输出信号,也可以用下面的结构表示,都是16位的定点数计算。

请问有什么好的办法实现?这里的意思就是 第一个数输入后,必须得到相应的u值(必须一一对应)才能输入下一数。

我觉得弄成逻辑的话,需要在一个时钟内完成两个减法和一个取整运算,这样是不是大大降低了时钟频率?

我看到有个文献说它是延时四个时钟得到一个输出,我不明白它怎么做到的

麻烦会的大哥给我讲讲。

伪代码是顺序执行,FPGA是并行的,你构造流水线,

第一周期做减法1,第二周期取整,第三周期减法2,第四周期又减法1,

这样,延时四个周期就可以有结果了。

这种结构用流水线就可以,不过要先量化

要先量化

顶一个

还是不太明白啊,还得让大哥讲讲 谢谢

Input a

Output b

Reg u =0.7

always@(posedge clk)

c<=a-u;

always@(posedge clk)

d<=c取整

always@(posedge clk)

e<=c-d

前三个周期时这样吗?第四个周期怎么做啊?

我不太懂 求大哥 讲讲详细一点 这里就是不能减错位 是一一对应的 就是100个输入 100个输出谢谢

不太懂哎 能不能帮我写个简单的伪代码 谢谢

看来我对流水线的理解还不够深

量化我知道 就是 这个流水线 怎么实现 我还是不太明白能不能帮我讲讲 谢谢

always @(posedge clk or posedge rst) begin

if(rst)begin

end

else begin

c<=a-e;

d<=c取整;

c1<=c;

c<=a-e;

end

end

输出为d

fpga里面不能取整的,要提前做好量化

这里面第二个减法你好像没用啊,就是算e的那个减法,还有为什么第一个减法要用两次啊?我问了一些人 说反馈结构没法用流水线

写几行,给小编抛个砖吧

part1:

temp <= k(i )- u;

temp_d1 <= temp;

temp_d2 <= temp_d1;

...

part2:

r(i) <= round(temp);

r(i)_d1 <= r(i);

...

part3:

u <= r(i)_dx - temp_dx;

x代表可以调整的时序,可以取合适周期的值即可

根据实际计算,仿真一下,对齐时序应该不是难事。

那个是敲错了,应该是求e的减法,另外反馈结果不能流水线好象是对组合logic而言,

将组合逻辑添加reg拆环路,就可以构成流水线了。

再另外看下了别人回复的,确实FPGA内不能直接取整,是要先量化。

我明白你的意思 但是这也不是流水线吧 输入的值必须先存起来 三个周期更新一个值 后面的计算都是一周期一次 对不对?这样我产生输入的值实际上速度也减慢了 比如我现在输入值产生的时钟是100M 但是后面计算部分的时钟实际上要300M 对吧?

你的这个意思 是不是 我输入的值必须先存起来 用一个计数器 等到计数3次的时候 才更新一个输入值 这三个时钟让后面的计算成功产生u值 这也不是流水线吧 实际上我产生输入值的时钟降低了3倍 对吧

小编的意思是正解哦