这样也算是锁存器吗?

- always @(posedge clk or negedge rst)

- if(!rst)

- A0=0;

- else if(counter==0)

- A0=~A0;

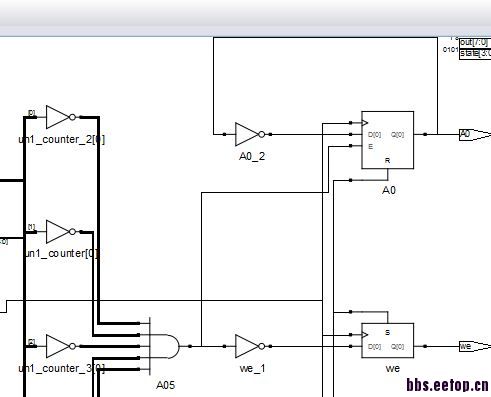

生成的RTL图如下:

可见,图片右上方的触发器中有一个使能端,即生成了锁存器;

如果把代码改为:

- always @(posedge clk or negedge rst)

- if(!rst)

- A0=0;

- else if(counter==0)

- A0=A0+1;

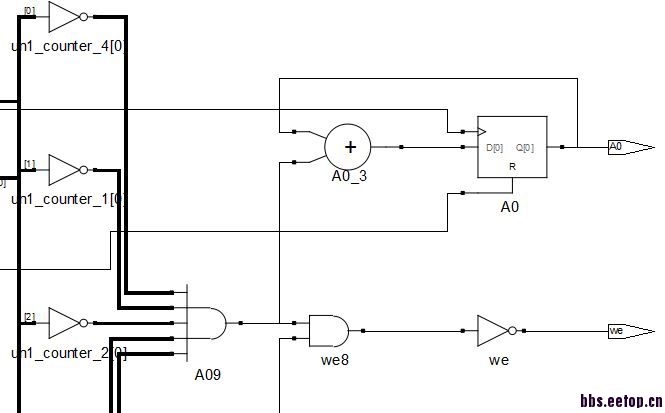

那么RTL图如下:

可见上图中不存在使能端,即没有锁存器生成;

可以这样理解吗?

锁存器的标准与危害到底是什么?

不是锁存器

RTL图所示的不是锁存器,

只是你这样的写法确实有可能产生锁存器,

一般如果有if,那么最后最好加上else,养成这样的习惯。

我一般理解为时序逻辑一般不会产生锁存器,

组合逻辑会产生锁存器,出现未考虑全面的条件时,就会产生。

比如,if或者case,没有写全所有的可能情况,

就会产生锁存器,所以最好加上else或者default。

两个都不算锁存器.

你的if语句里面还有个隐含条件,如果counter!=0 ,那么应该是什么输出?保留原值?要保留原值那就必须有一个en信号了

因为你有always@(posedge clk),带了时钟端口的,不会生成锁存器

这样写容易产生锁存器

时序逻辑不会出现latch,只有组合逻辑里面才有可能。

latch有可能会造成仿真结果和实际上板结果不一致。

带使能端,不代表会得到latch,做下去试试就好了

另外,先把“=”改成“<=”

哪只眼看到锁存器了?

那是带有使能端的DFF罢了

latch是活在组合逻辑的世界中的

非常感谢~我一直 =有一个问题,挺多人强调在时序逻辑中使用非阻塞型的赋值,但是我觉得这个得根据实际情况来看吧。如果在一个always语句中只对一个reg型变量进行赋值,那么无所谓是阻塞还是非阻塞。 另外我是这个认为的:在时序电路中,一般而言使用非阻塞赋值是错不了的;在组合电路中,无所谓使用哪种。

不知您如何看待。

推荐时序非阻塞、组合阻塞的一个原因在于,这样做可以使仿真行为和实际动作行为最大可能的一致

减少因为语言、语法带来的人为影响

P.S. verilog虽然相对要求灵活,但是基本的语法还是要遵守的,要不然会编译告错的

是否可以如此理解:1、在时序逻辑电路中,是不存在锁存器的,因为触发器本身就带有使能端,因此在if else语句中可以语句不充分;

2、在组合逻辑电路中,需要避免锁存器,但是有一个问题我一直不解:

- module latch1(cnt,a,b,c);

- input [1:0] cnt;

- input a,b;

- output reg c;

- always @(cnt or a or b)

- begin

- case(cnt)

- 2'b00:c=a;

- 2'b01:c=b;2‘b10:c=1;

- endcase

- end

- endmodule

在以上的程序中,当cnt为2’b11时,c不改变原值,但是这种情况下如何才能使综合后的结果中不会出现锁存器呢?