夏宇闻书上的一个例子说是模块会不稳定

module fboscl(y1,y2,clk,rst);

output y1,y2;

input clk,rst;

reg y1,y2;

always@(posedge clk or posedge rst)

if(rst)y1=0;

else y1=y2;

always@(posedge clk or posedge rst)

if(rst)y2=1;

else y2=y1;

endmodule

========================《Verilog数字系统设计教程》p195

但从条件上分析, 复位后,在没有发生有效时钟沿时, y1 = 0, y2 = 1;

case 1: 上面时钟先来, 所以上面先动, y1 <= y2, 因为y2还是1, 所以y1 也变成1

case 2: 下面时钟先来, 所以下面先动, y2 <= y1, 因为y1还是0, 所以y2 也变成0

这个模块也就无所谓什么稳定不稳定的问题,只是初始状态有点随机。

因为模块名字fboscl, 估计是模拟oscillator, osc初始状态随机,这是正常的。

当寄存器的Tco=0,数据路径延时=0时,你说的情况就可能会发生。但是这种假设有意义吗?CycloneII的LE_FF的Tco是300ps多。

什么乱七八糟的,现在的教材真是乱来,复位信号使能无意义,释放才有意义,所以释放都考虑同步释放复位,这个例子无任何实际意义

不客气地说,夏宇闻根本就是个江湖骗子……

他写的书乱七八糟,错误百出。即时写对的部分也有很多风格上是有问题的。

您说的很对,刚刚特意查了一下原书,确实是一个反馈振荡器的例子,但是书中已经很明确的写了,这个例子是用的阻塞赋值,下面还有一个非阻塞赋值的例子,两个例子作对比是为了说明阻塞赋值与非阻塞赋值的差别的,

小编只拿出来一半让人解释原因,容易让人引起误会

您说的也还算是符合事实.......夏先生的书代码风格确实不敢恭维,书中错误也着实不少......

但这个江湖骗子恐怕有些过了吧,至少我写信给夏先生,不过就是一封邮件,一二百字,反映一些书中错误和问题,顺便有些许讨教,却时常收到了上千字的回复,话语也算中肯和耐心,着实让我有点受宠若惊

至于错误,夏先生说年纪大了,部分翻译编写非本人亲自所为,校审也难免有所疏忽,再加上出版社排版和印刷问题,确实造成很多错误,对读者造成的不必要的困扰,深表歉意

虽然夏先生的书阅读起来确实会有各种不适应的感觉,我也不例外,但至少我觉得夏先生将近古稀之年还坚持翻译最新的国外书籍资料,这份心意还是值得肯定的

至于您么,八个字:管中窥豹可见一斑

什么叫无意义?正如前面所说,为了对比说明阻塞赋值与非阻塞赋值的区别,以及后面提倡时序逻辑用非阻塞赋值,组合逻辑用阻塞赋值,而有意引入的一个阻塞赋值会造成竞争冒险的例子,

您要是很有本事,是不是也写一本造福广大中国读者的教材出来?一定买一本拜读下

好吧,我收回他是江湖骗子的说法。

我只是看过一些他的书,不了解他的人。

如果说他是老学者的话,那也可以理解了。

只能说,他学的那套verilog,无论观念还是风格,跟现在主流的数字设计推荐的verilog风格,已经相差很远很远。

客观地说吧,他自己写的书真心不推荐看了,风格有问题,错误也多(不是排版印刷错误,本来就是错了)。

他参与翻译的一些外国书还可以。

就拿lz的这个例子来说,既然书名是《Verilog数字系统设计教程》,举一个模拟oscillator的例子,说实话我同意4楼的想法,确实挺奇怪的。

因为第一、数字电路设计不会用verilog搭oscillator,这个例子没什么现实意义;第二、数字电路会有工具保证setup和hold时序,lz所说的这个时钟早来几ps就怎样怎样的情况在实际电路根本不会出现。

我不清楚书上这个例子想帮助大家理解什么概念,个人觉得,如果目标是“verilog数字系统设计”的话,这个例子无论帮助你理解什么概念都是欠妥的。

我不知道你是学生还是工作了。如果你是学生的话,我只能说,以现在的高校教学,你先这么学着吧,以后到了公司里,再慢慢体会学校里学的东西哪些是错的。

呵呵 可怜的机械的教条主义的受害者,你是做设计的吗,有verilog tape-out的chip吗,把你这个所谓的例子电路丢到DC里看看什么结果,这就是中国写verilog的作者大部分的通病,忽略了硬件设计语言的本质,纠结在语法的小技巧里,十分怀疑这些人是否真的干过设计,看书的风格完全是从C语言跑出来的,甚至还见过直接把verilog 的IEEE标准拿出来直接翻译就当教材的,说他们是江湖骗子都是轻的,完全误人子弟。等你真干了设计,就会发现这些完全毫无意义。

写书就没什么必要了,我写的教材在公司内部做新人培训资料,你是没幸观摩了。

已毕业有些时日,马上就三字头了

其实小编举得这个例子的问题,在原书中是被放在深入理解阻塞赋值与非阻塞赋值一章,

夏先生在该章开始就已经说明,原型是国外的一篇论文,该论文作者是站在对综合器和仿真器内部原理深入理解的基础上写的,

至于采用振荡器这个例子,可能原文就是如此吧,也仅仅是为了解释阻塞和非阻塞的区别和可能造成的影响,而举得一个并不合理的例子

通过阅读全文,可以发现整篇内容充斥着各种阻塞和非阻塞使用的实例,有合理的,也有很多实例,正向小编所举的例子一样,是不合理的,会引起错误和竞争冒险,并从综合器和仿真器的内部原理部分解释了这些不合理甚至错误的产生原因,也多次强调即便类似这样的描述或许可以生成正确的电路,但依然可能导致前后仿真的差异,是不建议不提倡甚至是应当避免的

夏先生也说了翻译成中文并加入自己的理解编写而成,是希望在更深入的层次上理解阻塞与非阻塞赋值

另外该章节应该算是书中比较靠后的部分了,我个人觉得,对于初学者而言,可能都还不明白综合与形成实际电路的概念,这章的内容并不适合初学阅读,谨记组合逻辑用阻塞赋值,时序逻辑用非阻塞赋值就可以了,等对FPGA和硬件模型的描述有了一定了解以后再来阅读比较合适

最后想说的是,就现在的情况来看,夏先生的书确实不适合初学者阅读,错误不少,内容也稍显枯燥,再说多年前的书了,咱们也就别要求什么与时俱进了......

对于初学者,我觉得特权的书也还是不错的,至少图文并茂,有例程代码还有配套视频,可以板级验证实现,学起来能带动兴趣也就不觉得枯燥了,还有先锋,也还有黑金的那些事儿事儿事儿事儿和瞎搞不负责的那些笔记等等,活在现在这个时代,吸收着前人的经验,也是一件幸福的事~

可是,反过来,倒退十年?那个年代恐怕国内都没多少人用verilog吧,能找到这样一本(现在看来并不好的)中文书来看,已经是莫大的知足了

想看新东西,正如您所说,看些夏先生的中译版或者直接拜读英文原版,或者直接看厂商手册就好了

ps:中国教育制度,我也只能说呵呵了,另外夏先生恐怕是我见过的高校教师当中对当今教育制度鄙视至极的一位了,误导读者还是什么的暂且不说,至少以他的名望,貌似到退休都没有被评上博导,也能说明一些问题吧

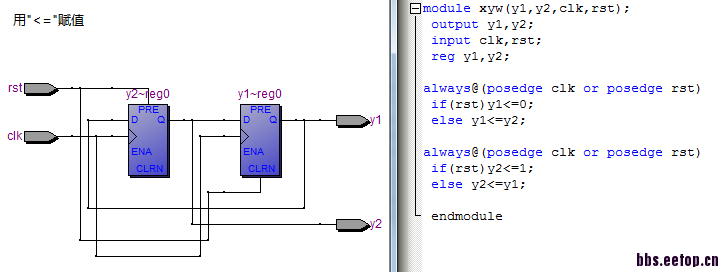

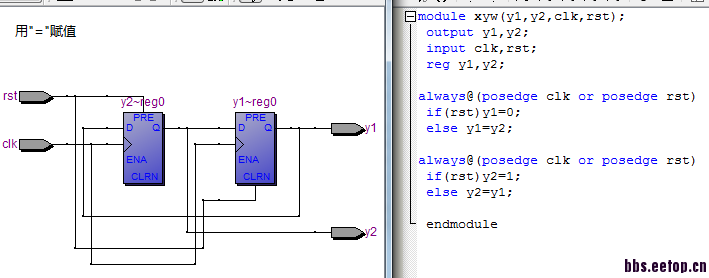

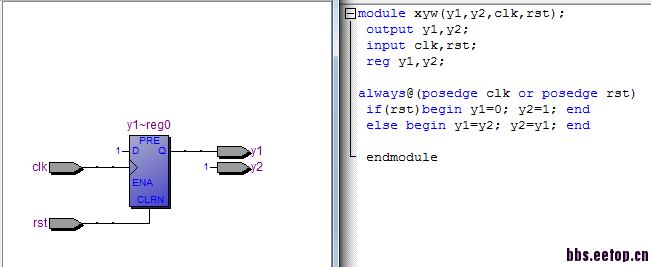

特意试了“<=”和“=”。Quartus II 11.0sp1,综合后的RTL电路和源码如下:

或许我说话有些言重了,那好吧,我也道个歉,

不可否认,您的话确实有道理,这个例子几乎没有实用的意义,原因楼上我刚刚解释了,该例子仅是老外为了解释阻塞非阻塞差别而有意引入的一个并不合理的例子,也说明了,这种时序逻辑使用阻塞赋值的使用方法是应当避免的

您说的:"忽略了硬件设计语言的本质,纠结在语法的小技巧里,十分怀疑这些人是否真的干过设计,看书的风格完全是从C语言跑出来的,"

您说的这个c的思想来分析,实际上在原文当中,是站在综合器和仿真器的角度来分析的,那么遇见阻塞赋值,就必然要把这两句y1=y2和y2=y1分出个先后顺序了,所以前仿真必然会出现与设计想法相悖的结果,当然这个结果仅限于前仿真,后仿真走的综合后电路模型,是不存在这个错误的

当然了这个例子到底具备什么样的实际意义?我觉得存在就有它的道理,可能我才疏学浅,不知道罢了,至少在这里,这个例子的存在意义说明了阻塞和非阻塞赋值在综合和仿真工具对实际电路分析中的原理和差别.

或许我年纪尚轻,也孤陋寡闻,接触的人也比较少,至少夏先生是我见过的不可综合的行为模块写的最好的,这一点也是我周围的人公认的,

至于夏先生的不足之处,不可否认,人无完人,

我不知道您对夏先生认识有多深,至少就我个人而言,我觉得我比您了解的多一些,先抛开书中错误和对人的误导,也抛开他的学术和项目设计与验证的功底,至少古稀之年还每日坚持翻译国外最新教材和书籍,这一点我是折服的,这份心应当值的肯定,

书中有错误就是误人子弟么?我不认为,难道仅凭这一个例子?况且这个例子出现的前因后果我也说了,一点也没有误导人,只是您以偏概全误解了

如果您能指出书中真的存在对硬件描述语言本质的严重误导,以我对夏先生的了解,他一定会邀请您去他家做客的

瘦死的骆驼比马大,再怎样,几十年的经验,不敢说方方面面都强于您,总有比你我认识深刻的地方,总是值得人尊敬和学习的

谦虚和尊重,尤其是对你并不了解的人,始终是一个好的品质

是的,这个例子当中阻塞非阻塞综合后电路是没差别的,后仿真也是一样的,差别仅在于前仿真,由于使用阻塞赋值会导致前仿真出错,因此时序逻辑要求使用非阻塞赋值实现,正如前面所说,即便这样描述可以综合出正确的电路,但应当避免这样描述

看大家说的都挺精彩的,批判和争论也是种学习啊!

还是10楼的方法最实在,你得看看综合出来的实际电路是怎么样的,根据电路来分析结果是最好的,光盯着代码看没意义,毕竟这是HDL不是C语言。

蒽,这是正路~

只是这段代码在原文中的原本用意并不是为了说明综合出什么样的电路,而是为了说明多个时序逻辑always块用同一个时钟触发,其内部用了阻塞赋值,且互相耦合,会对综合器和仿真工具的分析过程造成影响,会使前仿真结果出现不确定性,仅此而已,

并且也说明了为了避免这种不确定性的错误,不要在时序逻辑当中使用阻塞赋值,

但是这段代码里面,用阻塞赋值和非阻塞赋值的方式,综合出的电路是一样的。因为这段代码遵循了一个原则:在一个always块里面只对一个变量进行赋值,或者多个变量之间没有因果关系。这应该是HDL代码编写的基本原则吧。

有争论是好的,可以让概念更清晰, 不过最好限制在问题本事上。

我一开始并没注意到这个赋值的方式,个人觉得这是个很不好的书写习惯。

对应综合而言,always里的触发方式基本就决定了是组合电路还是时序电路,

所以在systemverilog里面,还特别增加了不同的always关键字。

对于DC综合,只要不在一个always里面混用两种赋值方法,都不会出问题。

但是如果养成这种赋值不规范的习惯,就容易出现混用的可能,导致综合出问题。

好的习惯一定可以避免很多低级错误, 所以有些坚持还是值得的。

这个例子是有些不妥的,如果要达到书上说的情况,只限于手工放置这两个寄存器,

一个离时钟源很近, 一个很远,造成hold violation;

如果用综合工具,很容易保证时序不会有问题,即便时钟有skew,造成有一个寄存器(DFF1)

先采到数据,但是因为hold time,采到的数据也不会立刻出现在DFF1/Q上而被

另外一个寄存器(DFF2)采到,否则DFF2就是漏掉了前一个DFF1/Q,这是hold violation.

可能作者在用这个例子说明自己的想法的时候,并没有考虑实现的问题。或许是作者觉得

交代太多的背景条件,会让很多初学者难以理解。但无论如何,应该找一个更恰当的例子才好。

蒽,综合后形成电路没差别,后仿真也没差别,

有影响的仅仅是前仿真或者该模块作为行为模块时,在仿真工具中运行时,由于会对同时变化互相耦合却使用了阻塞赋值的两个量分出个先后顺序关系来,因此会对仿真结果产生不确定性

当然,我也觉得这里用"几个p秒"来描述有些不妥,毕竟几个p秒对于实际电路同步时钟的影响来说恐怕构不成威胁,

实际上通篇阅读以后,可以明白原文的意图,理解其思想才是我们要做的,

至于这几个p秒么....毕竟老外的东西,翻译成中文难免有瑕疵.....咱们就放过它吧...........

蒽,您分析的很对,原文就是以此例为反例,说明这种赋值方式是不好的,会造成不确定性和时序违逆,因而不建议这样使用

后面紧跟着一个没有歧义的用非阻塞赋值实现的振荡器实例,小编没有贴出来而已,

人间自有真情在啊。这么多人回复。

嗯,有道理

no-block和block的区别。综合后一样,没有区别,前仿真可能会出问题。