怎么看一个设计的最大运行频率

时间:10-02

整理:3721RD

点击:

一般设计只考虑满足频率要求就可以了,但是怎么看一个设计的最大运行频率呢?求教

我是菜鸟,最大频率是不是综合的时候在报告里面就可以看到啊,就是能够跑到的最高频率吧,不知道对不对

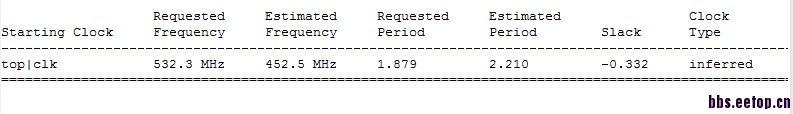

这是自动给出的结果,为什么SLACK有幅值呢?好像不是最大频率

从RTL看最大频率的话要估算出最长路径大概有多少级逻辑门,然后根据vendor提供的数据没一级逻辑门延时大概是多少,就可以算出最长路径延时,即可得最大频率;

一般使用综合工具结合来估算;最大频率跟你使用的verdor厂家的库有关;

看综合的report

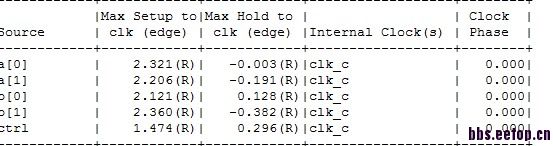

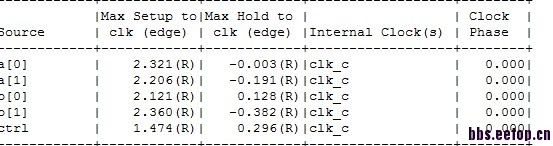

综合结果只需要看setup的slack不为负即可;不用关心hold的slack值

我用FPGA设计的,需要自己算频率吗

你看到的这个好像不是report吧,你看看report就可以看到最大时钟频率了

是这个吗?

RE

楼上分析的都很好,,,,,时序分析

fpga综合出来的延迟只是逻辑门的延迟没有线延迟,不准确;

需要进行完布局布线之后,查看timing时序报告,那里面给出的时钟频率,是带有延迟的,具有参考价值,结合这个时钟频率再做布局布线后仿真,才能最终确定你的设计的时钟频率。

根据布局布线给出的频率做参考设置仿真的频率吗?

功能仿真的频率随意设置, 布局布线后仿真的频率需要参考timing报告(布局布线后的报告)给出的频率来进行设置

综合完了以后有report

综合工具会报这个吧

但是我需要比较不同结构能达到的频率呢?