verilog行为级描述

时间:10-02

整理:3721RD

点击:

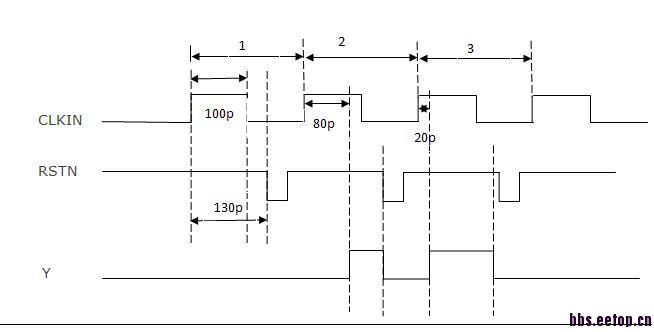

下面是两个输入波形CLKIN and RSTN,CLKIN的周期是200p.占空比50%,输出为Y..

Y信号是CLKIN在每个周期延迟不同单位而生成的。同时Y信号输出也受RSTN控制。如果RSTN=0, Y将置为0并保持到下一个周期开始。所以如果某个周期延迟超过130p,输出Y将始终保持为0。例如:在一二三个周期,要求的延时分别为150p,80p,20p, 输出Y如图所示。 求助如何写verilog行为级描述?

LZ确定200p的时钟?如果要写时序的话很简单啊,关键是这个时钟频率也太

5G时钟?

这特么得啥工艺啊

是闹着玩么?

时钟的数据只是作为参考

这个就叫行为级描述吧 ~?