关于数字pwm和sigma_delta噪声整形

时间:10-02

整理:3721RD

点击:

本人最近一直在研究sigma_delta调制器和数字pwm的算法实现,数字pwm最大的问题是对于44.1k的采样频率和16位的采样位数需要一个44.1k*65536的时钟,这几乎是无法实现的,所以需要用sigma_delta调制器噪声整形将位数压缩,将噪声推到高频处,那问题来了,是不是这个推到高频的噪声一直等到pwm输出后经过一个lc滤波器后才虑掉呢,还是在pwm之前经过一个低通滤波器虑掉呢?

还有很多资料我理解的应该是将滤波器放在pwm之后了,可是经过pwm的三角载波会不会将高频噪声带入信号频带内呢?

还有一个问题就是:sigma_delta调制器的阶数如何确定呢?是不是根据那些公式算出来,比如说增加一阶可以增加多少db的动态范围,然后根据公式计算位数截断后的动态范围与阶段前相同即可,对吗?

为啥没人回复我呢?继续等待!

依然是没人回答!

三角波只能将小于其频率一半的噪声带进来

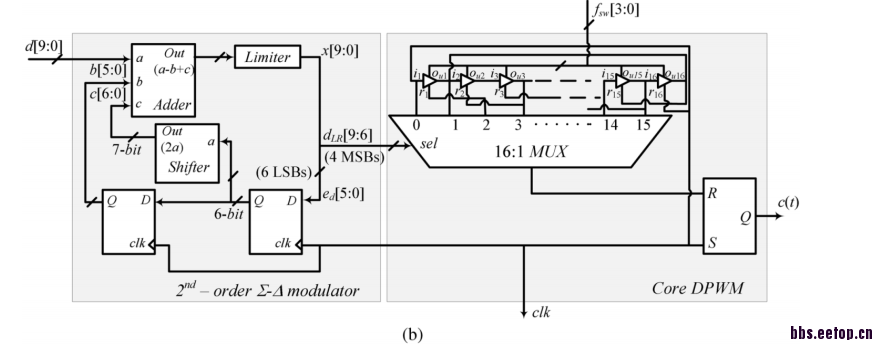

我前一段时间做了一个sigma-delta结构的PWM 在文献中读到的有大神可以达到10M的开关频率,我理解的sigma-delta结构实际上就是前面有一个快速计算的反馈电路,我理解的你的问题,16bit的pwm完全没有必要完全用sigma_delta结构实现,可以八位的sigma_delta,八位的delay这样会不会更容易实现一些?我也是新手,只是自己的理解,共同学习下,[attach]519973[/attach]