一个组合逻辑always@(<signal>)语句的测试(已解决,结论4楼)

求解:组合逻辑always语句的敏感信号为何会被综合器优化掉?

一个对组合逻辑always语句测试的简单代码,如下:

- reg out;

- always @(ctl)

- out = in;

综合后形成的实际电路结构,以及仿真波形却等效于如下代码:

- wire out;

- assign out = in;

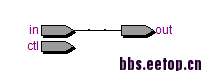

综合后控制变量ctl被优化掉了,实际电路如下:

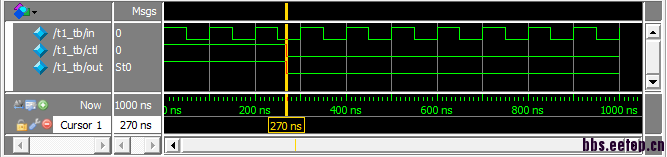

仿真波形如下:

前仿真:可以实现always @(ctl)中,敏感信号ctl对语句内代码的触发

后仿真:敏感信号ctl完全不起作用

Quartus+ModelSim /ISE 均是同样结果

求解:组合逻辑always语句的敏感信号为何会被综合器优化掉?

初步怀疑,如果使用always语句内部没有涉及到的信号做敏感信号,则综合时会被综合器直接砍掉……

完全失去代码本来目的.......

不知原因为何如此.求高手解答

初步怀疑,是否因为用always语句内没有涉及的信号做为敏感信号

源代码如下:

---------设计模块代码-------------------

- module t1(in, out, ctl);

- input in, ctl;

- output out;

-

- reg out;

- always @(ctl)

- out = in;

-

- // wire out;

- // assign out = in;

- endmodule

----------测试模块代码----------------

- `timescale 1ns/1ps

- module t1_tb();

- reg in, ctl;

- wire out;

-

- t1 t1_inst(

- .in (in),

- .out(out),

- .ctl(ctl)

- );

-

- initial

- begin

- in = 1;

- ctl = 1;

- #270

- ctl = 0;

- end

-

- always #50 in = ~in;

- endmodule

这是一个典型的不可综合的例子。对RTL设计没有理解。

out <= in ?

感谢提示,已解决

一直以为always语句必然是可综合的....实际情况有所差异

always语句被综合为实际电路时,尤其是组合逻辑,只会关注always语句内实际代码,而不会关注所谓的敏感信号列表,

最终有效触发信号只和实际综合后形成的最终电路模型有关,因此敏感列表不完整或者多余时,并不影响综合后电路,

仿真差异原因,前仿真执行会通过敏感信号列表触发,才执行内部逻辑,而后仿真则完全按照综合后和实际电路对应的网表文件执行,已经没有所谓的敏感信号了

与阻塞,非阻塞无关,不影响

以后直接用always@*来实现组合逻辑即可。

正解,括号内敏感信号是给编译器看的,最终生成的电路才是主要的。

如果要实现控制,用if else语句。

非常感谢~早上起来,您一句不可综合直接点醒我了,....

从接触verilog到几小时前,一直以来印象都是always是可综合的,从没怀疑过居然会不可综合.....一直纠结可综合为什么还会被砍掉........

您一句不可综合,恍然大悟,仔细想想,这种想在组合逻辑中,依靠X信号变化一次触发其他和X信号无关的信号传递一次的逻辑,在实际电路中应该是不可实现的,貌似只能老实的改为时序逻辑了......

另一个例子,

always @(*)

if(ctl)

out = in;

else

out = in;

ctl即便做了条件判断信号,但由于实际逻辑的原因,同样会被综合器优化砍掉,依然等价于

assign out = in;

问题讨论的够深入