哪位帮我看看这段Verilog代码?运行一下

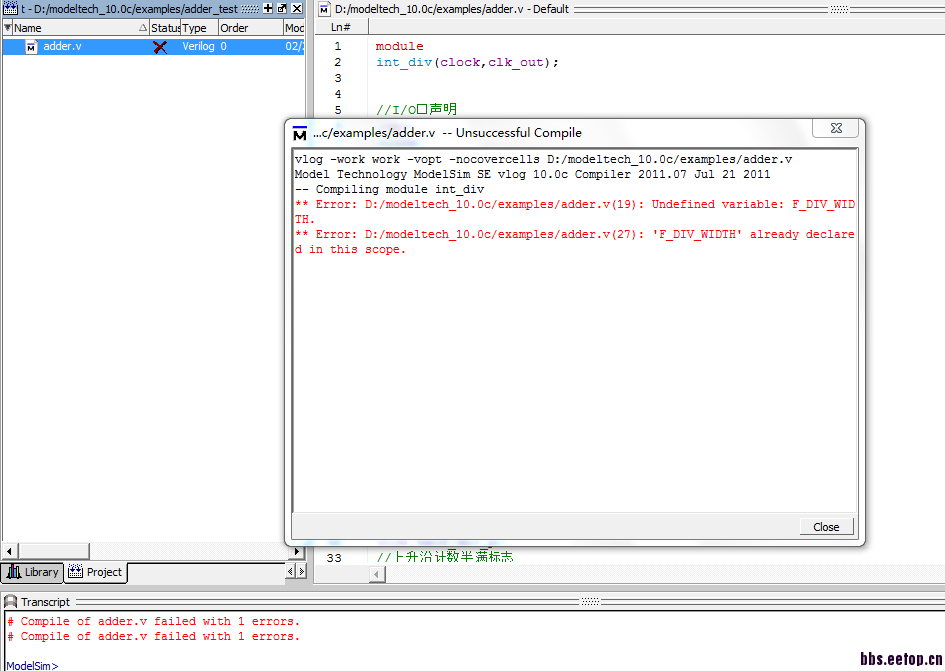

我运行的时候总是出现parameter那段有问题

这个基本功不是很扎实

帮我看看问题在哪

先谢谢了

module

int_div(clock,clk_out);

//I/O口声明

input

clock;

//输入时钟

output

clk_out;

//输出时钟

//内部寄存器

reg

clk_p_r;

//上升沿输出时钟

reg clk_n_r;

//下降沿输出时钟

reg[F_div_WIDTH - 1:0] count_p;

//上升沿脉冲计数器

reg[F_div_WIDTH - 1:0] count_n;

//下降沿脉冲计数器

//参数--分频系数

parameter F_div = 12;

//分频系数<<<<-----修改这里改分频系数

parameter F_div_WIDTH = 16;

//分频计数器宽度

wire full_div_p;

//上升沿计数满标志

wire half_div_p;

//上升沿计数半满标志

wire full_div_n;

//下降沿计数满标志

wire half_div_n;

//下降沿计数半满标志

//判断计数标志位置位与否

assign full_div_p = (count_p < F_div - 1);

assign half_div_p = (count_p < (F_div>>1) - 1);

assign full_div_n = (count_n < F_div - 1);

assign half_div_n = (count_n < (F_div>>1) - 1);

//时钟输出

assign

clk_out = (F_div == 1) ?

clock : (F_div[0] ? (clk_p_r & clk_n_r) : clk_p_r);

//上升沿脉冲计数

always @(posedge clock)

begin

if(full_div_p)

begin

count_p <= count_p + 1;

if(half_div_p)

clk_p_r <= 1'b0;

else

clk_p_r <= 1'b1;

end

else

begin

count_p <= 0;

clk_p_r <= 1'b0;

end

end

//下降沿脉冲计数

always @(negedge clock)

begin

if(full_div_n)

begin

count_n <= count_n + 1;

if(half_div_n)

clk_n_r <= 1'b0;

else

clk_n_r <= 1'b1;

end

else

begin

count_n <= 0;

clk_n_r <= 1'b0;

end

end

endmodule

不晓得你说parameter问题是什么,我这边编译通过,有三个警告。有什么问题剪切下来,别人才好看

不晓得你用什么编译器编译的 啊

你可以看看warning?我编译的问题图贴如下

Put parameter declarations before those who reference them

(For your case, count_p and count_n).

这两句怎么改?能贴出来吗

谢谢了

从代码上看应该没问题啊?

前面定义了count_p与count_n宽度为F_div_WIDTH 的reg型

后面才定义F_div_WIDTH为常量16

按你的说话先定义F_div_WIDTH为常量16后面再定义count_p与count_n,这样子也不行啊?

?

先parameter再申明reg

下一句:

assign clk_out = (F_div == 1) ? clock : (F_div[0] ? (clk_p_r & clk_n_r) : clk_p_r);

把F_div[0] 改为(F_div &1),试一下。

我记得paramter 不能直接移位。 F_div>>1,这样应该不行

module

int_div(clock,clk_out);

//I/O口声明

input clock;

//输入时钟

output clk_out;

//参数--分频系数

parameter F_div = 12;

//分频系数<<<<-----修改这里改分频系数

parameter F_div_WIDTH = 16;

//输出时钟

//内部寄存器

reg clk_p_r;

//上升沿输出时钟

reg clk_n_r;

//下降沿输出时钟

reg[F_div_WIDTH - 1:0] count_p;

//上升沿脉冲计数器

reg[F_div_WIDTH - 1:0] count_n;

//下降沿脉冲计数器

//分频计数器宽度

wire full_div_p;

//上升沿计数满标志

wire half_div_p;

//上升沿计数半满标志

wire full_div_n;

//下降沿计数满标志

wire half_div_n;

//下降沿计数半满标志

//判断计数标志位置位与否

assign full_div_p = (count_p < F_div - 1);

assign half_div_p = (count_p < (F_div>>1) - 1);

assign full_div_n = (count_n < F_div - 1);

assign half_div_n = (count_n < (F_div>>1) - 1);

//时钟输出

assign

clk_out = (F_div == 1) ?

clock : (F_div[0] ? (clk_p_r & clk_n_r) : clk_p_r);

//上升沿脉冲计数

always @(posedge clock)

begin

if(full_div_p)

begin

count_p <= count_p + 1;

if(half_div_p)

clk_p_r <= 1'b0;

else

clk_p_r <= 1'b1;

end

else

begin

count_p <= 0;

clk_p_r <= 1'b0;

end

end

//下降沿脉冲计数

always @(negedge clock)

begin

if(full_div_n)

begin

count_n <= count_n + 1;

if(half_div_n)

clk_n_r <= 1'b0;

else

clk_n_r <= 1'b1;

end

else

begin

count_n <= 0;

clk_n_r <= 1'b0;

end

end

endmodule

这样语法可以过,功能没时间看