verilog 存储器赋初值和输出

时间:10-02

整理:3721RD

点击:

各位大神,小弟写了一个存储器的小程序,但仿真结果却不对,不知为何,请指教

`timescale 1 ns/100 ps

module test_memory(clk,rst,out);

parameter LENGTH=20;

input clk,rst;

output [3:0] out;

reg [3:0] IX1 [0ENGTH-1];

integer i,j;

always @(posedge clk)

if(!rst)

begin

j<=0;

for(i=0;i<LENGTH;i=i+1)

IX1[i]<=i+1;

end

else

begin

IX1[j]<=IX1[j]^4'b0010;

j<=j+1;

end

assign out=IX1[j-1];

endmodule

后仿

`timescale 1 ns/100 ps

module test_memory(clk,rst,out);

parameter LENGTH=20;

input clk,rst;

output [3:0] out;

reg [3:0] IX1 [0ENGTH-1];

integer i,j;

always @(posedge clk)

if(!rst)

begin

j<=0;

for(i=0;i<LENGTH;i=i+1)

IX1[i]<=i+1;

end

else

begin

IX1[j]<=IX1[j]^4'b0010;

j<=j+1;

end

assign out=IX1[j-1];

endmodule

谢谢你的回答,但我觉得那不是根本问题 问题可能出在输出方式上 但我现在还没搞明白

程序改过以后可以输出正常结果了

`timescale 1 ns/100 ps

module test_memory(clk,rst,out);

parameter LENGTH=20;

input clk,rst;

output reg [3:0] out;

reg [3:0] IX1 [0ENGTH-1];

reg [4:0] i,j;

always @(posedge clk)

if(!rst)

begin

j<=1'b0;

for(i=1'b0;i<LENGTH;i=i+1'b1)

IX1<=i+1'b1;

end

else

begin

out<=IX1[j]^4'b0010;

j<=j+1'b1;

end

endmodule

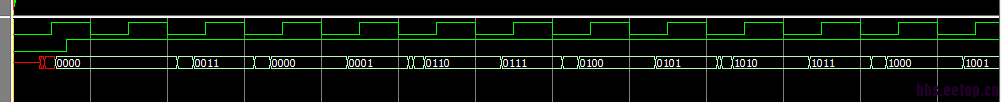

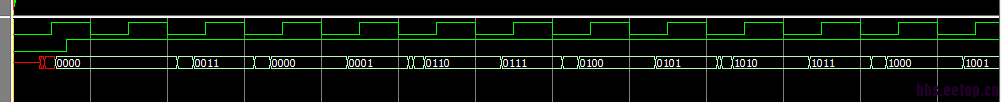

这时前仿结果

[attach]499351[/attach]

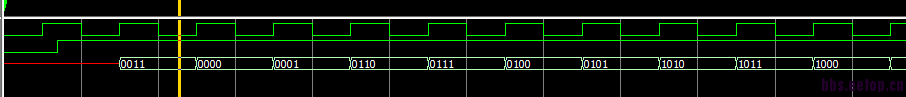

这时后仿结果

[attach]499352[/attach]

但感觉后仿延迟好大

前仿

后仿

后面对了应该是因为j的变量类型改为了reg,当j为整型时,out=IX[j-1]可能会有问题(j=0时,j-1为负数,超出IX的范围);后仿的话如果是读数据,应该存储器后面会接大的组合逻辑,所以都会有比较大的延迟,应该是正常现象