请教如何去毛刺

时间:10-02

整理:3721RD

点击:

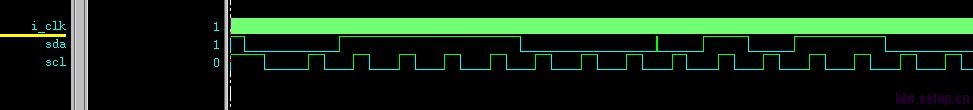

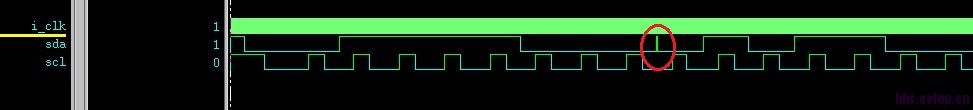

请教,如何消除上图中的毛刺,在做I2C的时候,SDA上产生一些宽度小于3个脉冲的高电平。请问如何消除

看来只有3个寄存器delay,然后&了

控制好双向口,不释放时别释放总线,如果不行,用D触发器可以滤毛刺

Is your design a master or slave?

It seems the glitch appears right before the ACK bit.

Since the bus is externally pull-high, the glitch shows the transmitter releases the bus 3us earlier than the receiver takes over.

It may look ugly but it won't affect its functionality.

呵呵,的确是看起来太ugly了,master和slave都是我设计的

D触发器滤毛刺指的是什么呢?

D触发器可以消除输入信号跳变造成的输出端的毛刺现象

这个不是传统意义上的毛刺,是SDA上的两个周期的脉冲信号,不能怎么用D触发器消除?

脉冲周期少的话用几个DFF级联,多的话就用一个计数器做DFF使能端

看看先