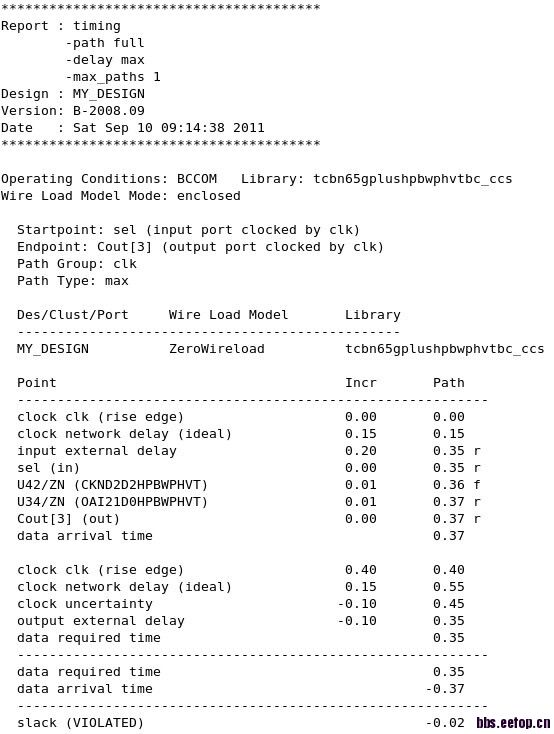

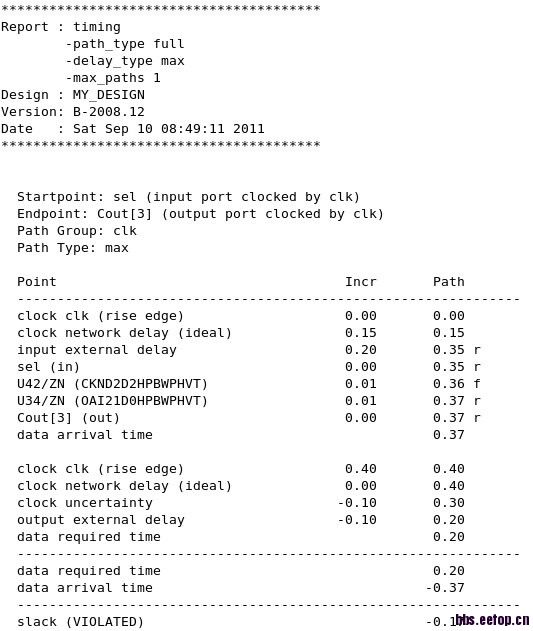

primetime和dc中STA分析差异

从图中可以看出,结果不同主要是由于dc计算data required time考虑了clock network delay (ideal),而pt计算data required time时没有考虑clock network delay (ideal)。问下各位大牛,真正的情况应该是怎么样的?我更感觉dc计算的结果是正确的。如果要将pt中结果改成和dc一致,是否要加什么代码?

注:约束都是一样的。critical path是从sel到Cout[3]之间的路径。

综合的时候,clock是ideal network,所以delay应该是0。

pt一般在pr之后,这时候的clock是真实的clock。

DC的时序分析只是对setup time而言的,而且只能作为参考。

但是在dc中STA分析时,那个delay不是0,在pt分析时是0。而且在计算data arrival time时无论pt还是dc都是考虑到了clock network delay的。

对于检查setup time这点我知道。但是还是对这个问题不大清楚,麻烦能不能说清楚点?

而且好像pt在pr之前也是需要做的,只是作为一个参考,主要是由于rc延迟的不精确,而在pr之后就比较精确了,是不是这样?

DC是不会考虑clock延迟的,所以DC综合之后,clock的延迟为0才对。

意识就是时序约束中加的uncertainty和delay在STA分析的时候是没有用的?

could you say it more clearly?

(1) syn的时候 加clk约束为 ideal clk了吗?

(2) 我怎么觉得你现在用PT跑的design并没有加入CTS?

学习一下!

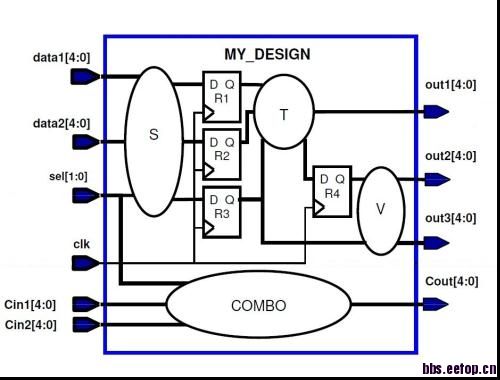

为什么cout 会有用clk来算setup?不是都是组合逻辑么

帮顶帮顶

与clock propagation的属性有关,pt理论上不会用你设的clock network delay,因为那个不是最终的。pt会用抽出来的delay。可能你用pt的时候还没有cts的信息,所以抽出来是0.

学习一下

小编是否没有加入“set_ideal_network clk”?如果只是p&r之前的sta的话建议加上,这样dc和pt的分析就能一致了。

network delay是怎么设上去的? set_clock_latency 还是什么? 然后具体看一下。

在DC综合的时候 就是用的uncertainty和latency来设置network delay的啊

在PT中也是这样设置的