关于跨市钟域

时间:10-02

整理:3721RD

点击:

如果数据跨时钟域,但是两个时钟域的时钟不是倍数关系,比如一个30M,一个100M,这种情况下是不是

要用FIFO隔离?除了用FIFO隔离还有其他的方法吗?

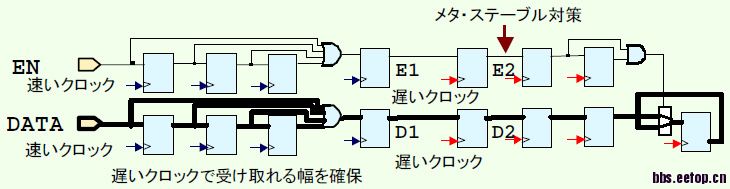

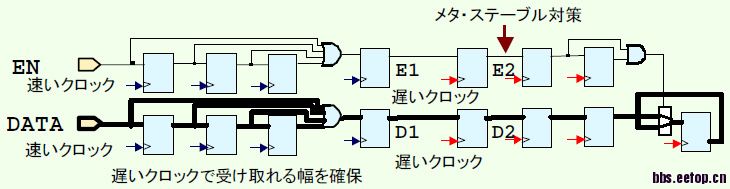

从100M过度到30M:(蓝色的是100M,红色的是30M)

感觉时钟只要大于一定的倍率(3倍),是不是整数倍没关系的。

要用FIFO隔离?除了用FIFO隔离还有其他的方法吗?

格雷码!

当然FIFO是最安全的办法!

很多种方法,完全可以与倍数关系无关,只要保证接受方能正确采到就行。可以在网上搜一下 跨时钟域设计 ,关于由慢到快,由快到慢,signal,bus传输的区别,等等,都有很多资料。

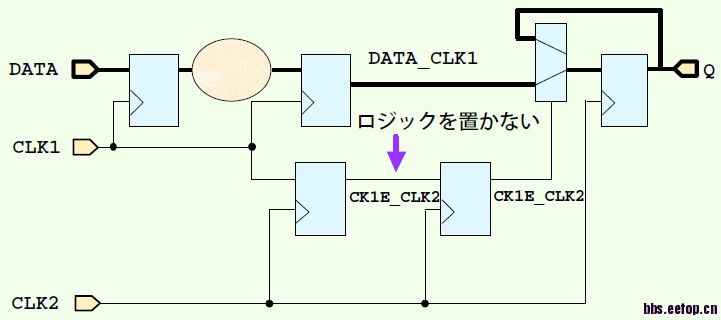

从30M过度到100M:(CLK1是30M,CLK2是100M)

从100M过度到30M:(蓝色的是100M,红色的是30M)

感觉时钟只要大于一定的倍率(3倍),是不是整数倍没关系的。

格雷码的方法是什么方法?是不是读写时钟是倍数关系的时候用block ram,不是倍数关系的时候

用fifo?

orlye:这个图有没有对应的verilog代码?另外你说要大于3倍关系,就和是不是整数倍没有关系了,

如果小于3倍就必须是整数倍关系吗?