关于xilinx ip核中乘法累加器mac的延迟问题

时间:10-02

整理:3721RD

点击:

最近用到了乘法累加器,利用了mac的ip核来实现乘法累加,实验结果倒是很正确,但是关于其中的延迟我觉得有点不太明白。

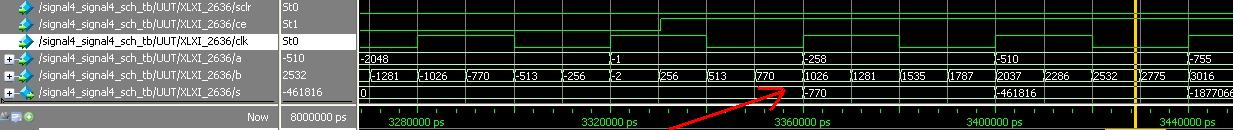

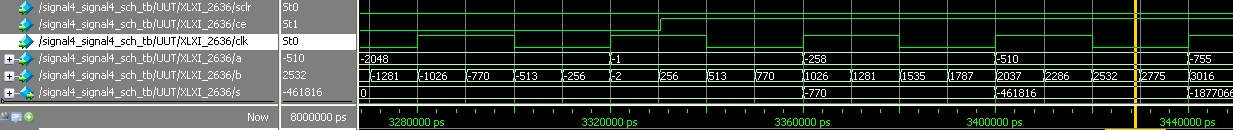

如上图所示,时钟使能后在第一个时钟上升沿处实现乘法,显然是770*(-1)=(-770),结果很对,但是感觉这里貌似没有任何时钟延迟啊。在配置IP core时是设计成latency=1的,但是在测试中却没有看到时钟延迟。我比较怀疑对于乘法累加能够在没有时钟延迟下完成吗?除非这里变成了组合逻辑,但是按理来说此IP core应该是用时序逻辑的吧?

在datasheet里面看到mac的IP core是利用一个dsp48实现的,我单纯测试一个dsp48,发现是有3T的时钟周期延迟(不同时钟周期可能有差别),那为什么用dsp48构造的mac却可以不用延迟呢(名义上配置了latency=1的)?

非常感谢。

后面不知道为什么又出现一幅图了,只看前面的图。

"利用了mac的ip核来实现乘法累加" 是指例化乘法的IP核吗?还是用代码?

如果是前仿真,也就是通过代码实现的话,是按照verilog的语法原则来仿真的,不会有所谓的延时。

就是编写test程序来测试该mac核性能的,按照我的理解,乘法器累加和输出一般应该要在开始进行第一次时钟上升沿之后几个时钟周期后按照流水线输出结果的,而dsp48硬件乘法器也确实是这样的,而xilinx自带的IP core中的mac就是利用dsp48配置出来的,但是测试时却没有任何时钟延迟,直接在第一次时钟上升沿后输出累加结果,有点类似于组合逻辑了,这个让我觉得不太可能。

这个就是打一拍(也就是latency为1)出来的啊

如果latency为零的话(纯组合逻辑),那么在b为770时,那么s应该立即为-770。这才是组合逻辑