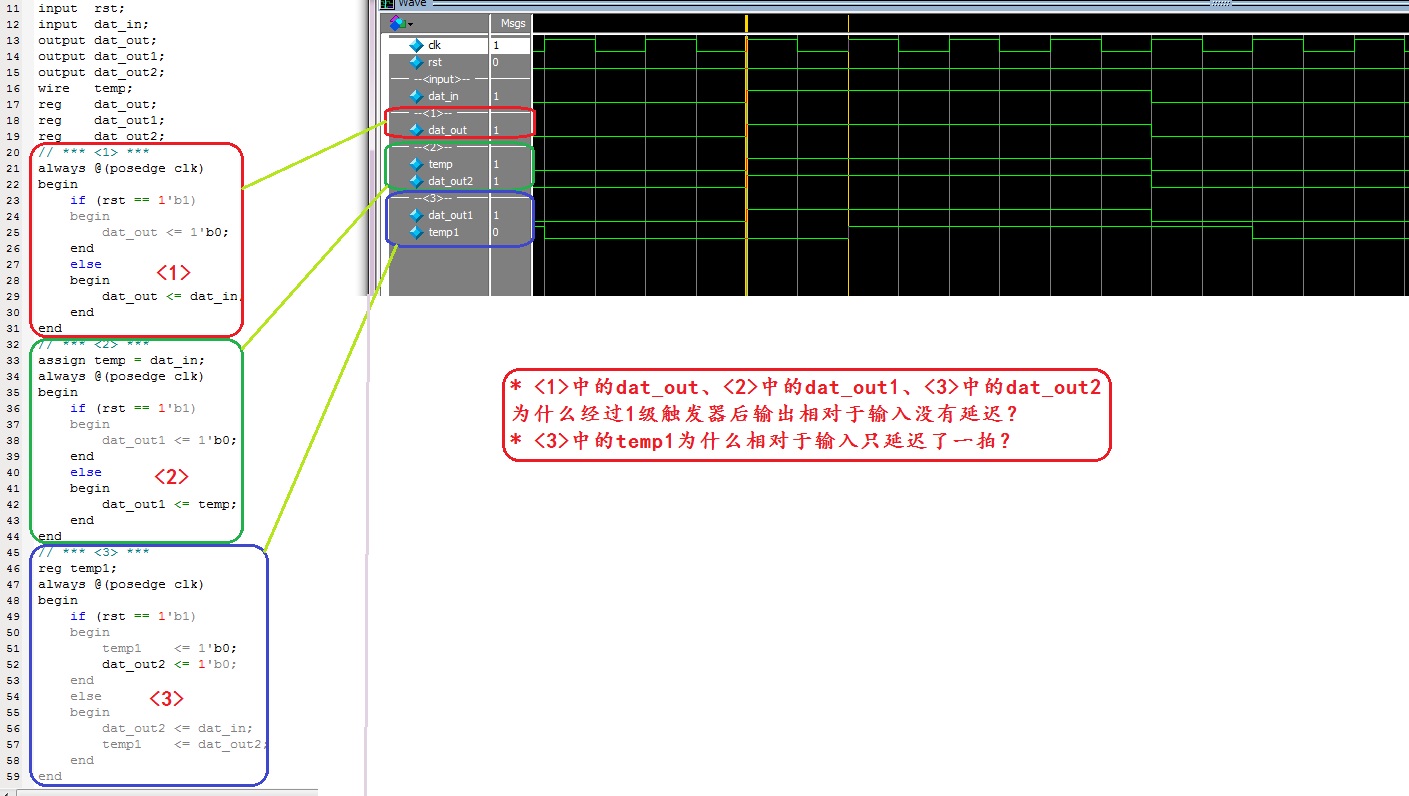

实际应用中非阻塞赋值问题

时间:10-02

整理:3721RD

点击:

详见附图。

这是仿真器的问题,你换VCS仿真试试看,结果可能不一样。

主要是因为仿真器对于上升沿的采样点判断,事实上对于你这里的波图,dat_in仿真器可以认为setup time为0而不采样,也可以认为足够而采样(这里就是采样了)。如果dat_in的上升沿不采样的话,你看起来会清晰多了。建议你在driver输出dat_in的时候加上 #1 延迟,另外,代码中的flop加上#1 延迟也是方便仿真调试的一个好习惯。

嗯,谢谢。

多谢指教