关于Verilog并行运行的问题

时间:10-02

整理:3721RD

点击:

- module cnt10(clk,rst,en,add_sub,q,cout); //十进制计数器

- input clk,rst,en,add_sub;

- reg [3:0]q1,q2;

- reg c1,c2;

- output reg[3:0] q;

- output reg cout;

- always@(posedge clk or posedge rst)

- if(rst)

- begin

- q1<=0;

- c1<=0;

- end

- else

- if(en==0)

- if(add_sub)

- if(q1==9)

- begin q1<=0; c1<=1; end

- else

- begin q1<=q1+4'b0001; c1<=0; end

- else //实现倒计时

- if(q1==0)

- begin q1<=9;c1<=1; end

- else

- begin q1<=q1-4'b0001;c1<=0; end

- always@(posedge clk or posedge rst)

- //实现秒表功能

- begin

- if(rst)

- begin

- q2<=0;

- c2<=0;

- end

- else if(en)

- if(add_sub==0)

- if(q2==9)

- begin q2<=0; c2<=1; end

- else

- begin q2<=q2+4'b0001; c2<=0; end

- end

- always@(posedge clk) //秒表和倒计时互相转换

- begin

- if(en)

- begin q<=q2; cout<=c2; end

- else

- begin q<=q1; cout<=c1; end

- end

- endmodule

- module cnt6(clk,rst,en,add_sub,q,cout);

- input clk,rst,en,add_sub;

- reg [3:0]q1,q2;

- reg c1,c2;

- output reg[3:0] q;

- output reg cout;

- always@(posedge clk or posedge rst)

- if(rst)

- begin

- q1<=0;

- c1<=0;

- end

- else

- if(en==0)

- if(add_sub)

- if(q1==5)

- begin q1<=0; c1<=1; end

- else

- begin q1<=q1+4'b0001; c1<=0; end

- else //实现倒计时

- if(q1==0)

- begin q1<=5;c1<=1; end

- else

- begin q1<=q1-4'b0001;c1<=0; end

- always@(posedge clk or posedge rst)

- //实现秒表功能

- begin

- if(rst)

- begin

- q2<=0;

- c2<=0;

- end

- else if(en)

- if(add_sub==0)

- if(q2==5)

- begin q2<=0; c2<=1; end

- else

- begin q2<=q2+4'b0001; c2<=0; end

- end

- always@(posedge clk) //秒表和倒计时互相转换

- begin

- if(en)

- begin q<=q2; cout<=c2; end

- else

- begin q<=q1; cout<=c1; end

- end

- endmodule

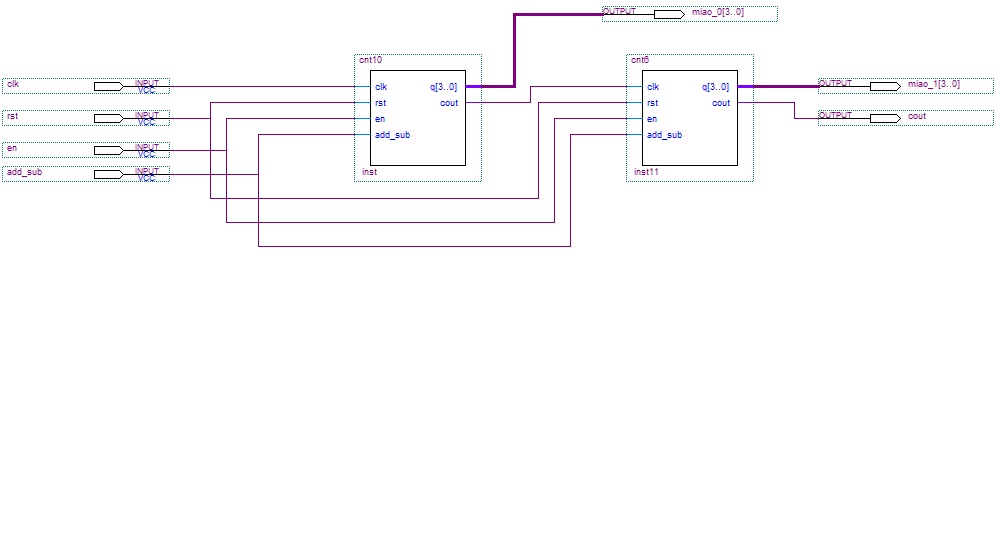

综合模块

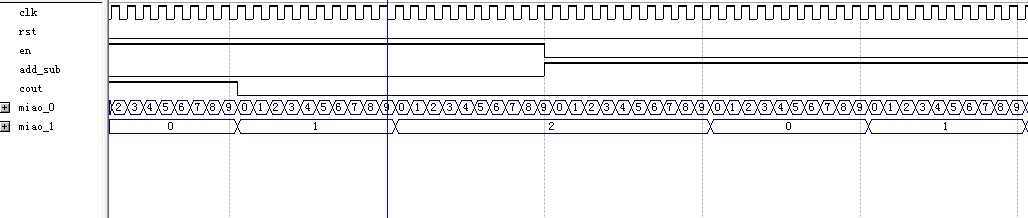

仿真波形

thanks for sharing

把 begin/end加 全,

一般begin ...end没有加好,他会报错的。但他没有

YOU ARE WELCOMEthanks you

真的,把begin,end加全了。报错是因为begin/end缺了一个,缺了一对不会报错,但可能导致软件对你的代码理解错误。

我觉得是不是仿真不稳定啊.之前如果是在en=1,add_sub=0变成en=0,add_sub=1之前,先让add_sub=1,就不会了。后来又不对了!

你的说明非常不清楚,不过我试着猜一下。你把“if(q1==9)”这些条件改成“if(q==9)”,看看是不是你想要的结果

设计错误!

虽然,在en=1,add_sub=0和en=0,add_sub=1这两种情况下,都是相同的加计数,但是你所写的代码中却使用不同加计数逻辑,这样就造成进位不统一,所以在两者切换的情况下,就不会有进位产生(前提是,要产生进位的情况下)。

建议:使用统一的寄存器,并且将en和add_sub拼接起来,使用case语句

注:

{en,add_sub}

2'h0 : 减计数

2'h1,2'h2 : 加计数

default : 保持

一定不行,q在这里是输出端口,他可以选择q1输出,也可以选择q2输出。而关于en==1与add_sub==0是作为秒表。而en==0,add_sub==1是产生60进制,因为下一个模块没有PO上来,其实他产生的进位是作为分钟的时钟信号的。en==0,add_sub==0是作为倒计时的。