verilog的问题

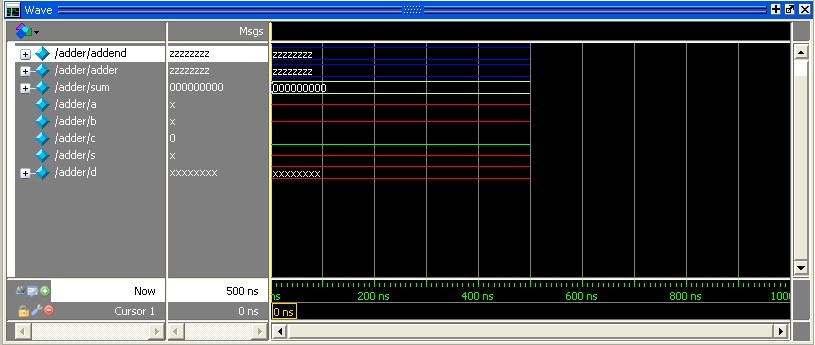

小弟初学verilog编了个8位加法器,编译通过、但是仿真不对、加数和被加数却都是高阻、求大神帮助。附上三段代码

testbench:

`timescale 1ns/1ns

module testbench;

reg[7:0]addend,adder;

initial

fork

addend=8'b00001111;

adder=8'b00010001;

join

add

testbench(.addend_a(addend),.adder_a(adder));

adder

test(.addend(addend),.adder(adder));

endmodule

add:

module add(a,b);

output

a,b;

reg[7:0]d,addend_a,adder_a;

reg a,b;

always@(addend_a or

adder_a)

fork

d=8'b11111111;

while(d)

begin

a=addend_a[0];

b=adder_a[0];

addend_a=(addend_a>>1);

adder_a=(adder_a>>1);

d=d<<1;

end

join

adder

add(.a(a),.d(d),.b(b));

endmodule

adder:

module

adder(adder,addend,sum);

input[7:0]addend,adder;

output[9:0]sum;

reg[9:0]sum;

reg

a,b,c,s;

reg[7:0]d;

initial

begin

sum=10'b0000000000;

c=1'b0;

end

always@(d)

begin

s=(~a)&(~b)&c+(~a)&b&(~c)+a&(~b)&(~c)+a&b&c;

c=a&b+a&(~b)&c+(~a)&b&c;

sum[8]=s;

sum[9]=c;

sum=sum>>1;

end

endmodule

内容不太懂你这样写的意思,建议你看看verilog的语法,没有信号是由于testbench中调用的端口问题吧,而且在adder模块中d是干嘛的,在你的程序运行过程中d回发生变化吗?

d其实就是为了能够使位相加循环、这样循环8次、如果要综合的话、不能用repeat()还有for语句的吧、我也是初学额、

似乎设计代码里面不能用fork...join包括语句吧,也是不可综合的吧。

fork...join和begin...end不是一一个性质的东西么、我还没综合过、仿真都过不了

fork join 一般不能用在RTL coding中,可以用在TestBench里面;begin end在RTL coding里面相当于C语言里的{ }

这样啊、起初在add里面用fork。join是因为想在给d赋值的同时、while能够触发、那要是去掉fork。in,always这个顺序块如果先给d赋值、那么while是不是就触发不了了、是不是得重新改语句了。

没看懂):

问题:adder add(.a(a),.d(d),.b(b));

这样写不对吧,adder中的端口名字为:adder(adder,addend,sum)

不是a, d, b;这样也能编译过去?

运行肯定是不对的;

fork join是并行语句加入,如果是想按时序的话还是用begin end更好,相当与一对括号

中间寄存器不能参与调用的么?

其实我应该加解释的、这样的确蛮难看的、

你把always block的觸發條件寫在自身的block body内,結果就是無法觸發,當然不會有值。

最重要的一点就是对HDL代码对实际元件的反映不太了解,还是没有HDL设计的经验,多看看参考书关于设计方面如何编码的吧。

建议你先看一下verilog的语法书,再看看代码风格之类的手册,语法书上应该有加法器的代码吧,可以对比一下看看; 另外,verilog HDL是硬件描述语言,所以写代码的时候,最好清楚自己写的verilog是在描述什么样的硬件电路。简单来说,不要用软件的思想来用verilog描述出来,而是先有硬件电路,然后再用verilog描述出来~

有道是大巧不工,真正能合成電路的用的語法都是很簡潔的。你自己看得懂,team mates 也看得懂。

恩、谢啦、