请教一个小白问题

时间:10-02

整理:3721RD

点击:

请问数字前端RTL代码的设计与时序有关吗?还是只是功能设计?要想保证前端设计的电路时序上冗余度是在用DC综合之后才能发现对吗?

而这个时序的冗余度是要依靠芯片制造厂提供的库的模型的对吗?

我的意思是想请问要做更快的数字电路,依靠的不是前端RTL代码,而是依靠工艺公司的工艺水平和DC综合优化水平,很少依靠RTL代码的修改对吗?

如果时序跟RTL代码有关,那要从RTL哪些方面入手去修改来获得更好的时序呢?

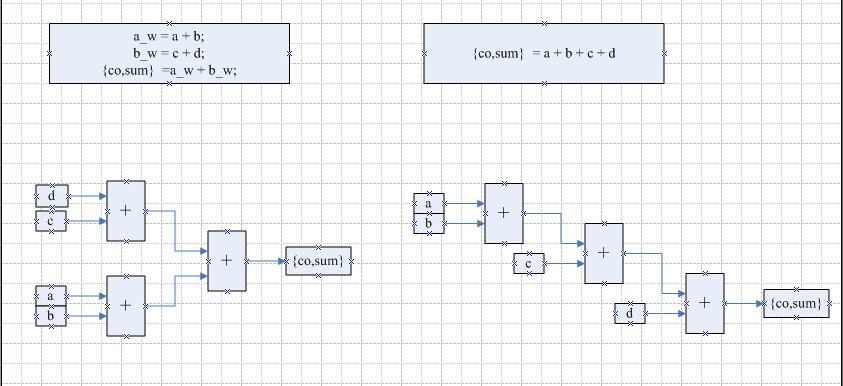

左边的速度就要比右边的快,这就是RTL代码增加速度

至于工艺上的加速,应该是减少逻辑器件的延时,使整体的耗时减少

回答的有点简单,我的经验也不多,相互学习学习

而这个时序的冗余度是要依靠芯片制造厂提供的库的模型的对吗?

我的意思是想请问要做更快的数字电路,依靠的不是前端RTL代码,而是依靠工艺公司的工艺水平和DC综合优化水平,很少依靠RTL代码的修改对吗?

如果时序跟RTL代码有关,那要从RTL哪些方面入手去修改来获得更好的时序呢?

这个是跟RTL有关系的,跟工艺也有关系

只不过是提升的效果不一样

请问可以讲讲原理或者举个例子吗?谢谢

左边的速度就要比右边的快,这就是RTL代码增加速度

至于工艺上的加速,应该是减少逻辑器件的延时,使整体的耗时减少

回答的有点简单,我的经验也不多,相互学习学习

RTL代码只是把电路描述出来而已~而系统、电路的架构,是数字IC前端设计的核心,2楼说的也是电路架构的问题, 如果更细说,对于“+”,还可以研究用什么样的加法器~当然,这个要看DC和PT的结果~

2楼正解

多谢,受教了

从器件的基本组成入手,减少设计中逻辑路径LUT的个数,可以提高整个电路的速率

RTL 主要是完成功能上的设计, 当然基本时序方面你要满足.比如 信号1 一定要在下个时钟的信号2完成后才能有效.

时序问题在综合后才能发现, 工艺决定器件的Delay,setup time ,hold time 等, 做时序分析就需要这些.