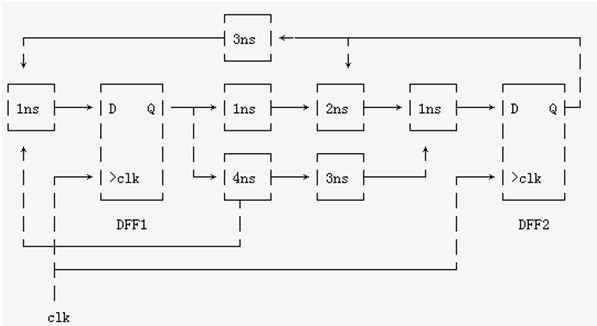

时序分析 关于skew 求人解答!

1、

关于setup/hold time

1)

假设存在positive clock skew为10ns,问最高电路频率

2)

能容忍的最大positive clock skew

3)

能容忍的最大negative clock skew

positive clock skew:DFF2的clock比DFF1的来的晚

negative clock skew:DFF2的clock比DFF1的来的早

Tsetup=1ns

Thold=1ns

Tclk->q=1ns

还可以

第一问中Tlogic+Tclkq<T+Tskew-Tsetup

Tlogic 最大值为4+3+1=8ns

Tclkq=1ns

Tsetup=1ns

所以8+1<T+10-1

得到T>0,奇怪?不知道算法是不是正确?

setup 是对的 但是hold不满足

4<10

所以是不能工作 最大工作频率是0

对于D1 Tmax=Tmin=5 不用分析skew

对于D2 Tmax=Tmin=3 不用分析skew

对于D1->D2 Tmax=8 Tmin=4

对于D2->D1 Tmax=4 Tmin=4

Launch 与Capture延的差值就是Skew。

Skew大好,还是小好?

只要Timing满足,Skew=0最好。

(1) 问最高工作频率,且clock skew只是假设,所以不用分析hold constaint. 得到最大工作频率62.5MHz.

(2) 只需要分析hold constraint. 得到最大positive clock skew=4。

(3) 只需要分析hold constraint. 得到最大negative clock skew=4。

1。设D1的clk为0ns,则D2的clk为10ns,总共4条路径,分析setup(max_delay)

D1->D2,

D1->D1,

D2->D2,

D2->D1,

分别计算data_arrival_time 和 require_time, 得出cyc>16ns, 所以最快62.5MHz

2和3同理,分析hold(min delay)

都是4ns

关于第一问 hold 不满足 不能打入触发器 不能工作啊

那只能是这个题目本身有问题。这样的话,就看题目考察的重点了。

实际项目中,setup和hold肯定是同时关注的。

5、7、8楼正解,列出所有路径分析。

牛人,还可以啊

很好,谢谢分享