请教大家818下面的问题的。-------版主-------在哪里?

时间:10-02

整理:3721RD

点击:

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

sum <= 0 ;

cout <= 0 ;

sum_p <= 0 ;

end

else begin

{cout,sum} <= a + b + cin ;

#5 sum_p <= a + b + cin ;

end

end

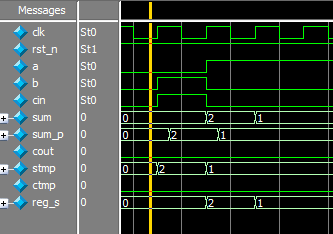

为什么在sum_p前面加一个延迟,结果在当拍延迟5个时间单位就出来,我觉得应该在下一拍延迟5个时间单位出来,我想的和仿真的结果不一样,求高人解答啊?

不懂,貌似都成线的赋值了!我觉得也应该是下一个时钟周期才延时5个时钟单位后赋值

帮忙顶一下5个timescale赋值

这个写法应该表示成了在当前时钟点上过5个timescale的时间后取a,b,cin的值后计算赋给sum_p

如果换成以下可能会满足你的要求

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

sum <= 0 ;

cout <= 0 ;

sum_p <= 0 ;

end

else begin

{cout,sum} <= a + b + cin ;

sum_p <= #5 a + b + cin ;

end

end学习了

你把延时#5放在当前的posedge clk 里面always块里,这样肯定是当前开始延时5个周期啊

这样可以,我试过。但就是不明白为什么会出现那张状况?

为什么啊,有点不明白,能不能细说一下,请教了。