关于AXI总线和Avalon总线的讨论贴

时间:10-02

整理:3721RD

点击:

最近需要写一个AXI到Avalon的桥,由于我之前没有接触过系统总线,所以把两种总线协议都看了一遍,但是AXI协议的图实在是太少了,所以由很多疑问,还请大家不吝赐教

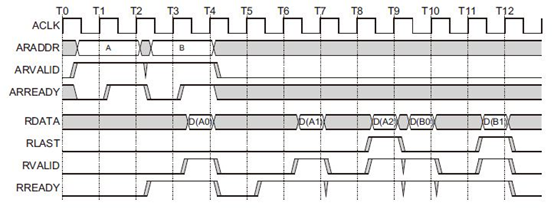

AXI读时序

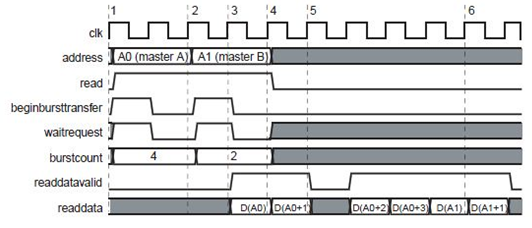

Avalon读时序(从端口)

从上面两个时序图都可以看出,两种总线都支持在一个burst未完成的情况下接收下一个burst地址,这里称之为传输挂起

Avalon总线协议里明确标出了这个时序图是从端口的时序,从图上可以看出,两个burst来自不同的master。AXI总线没有注明是从端口还是主端口。

我的疑问是,一个master的端口也会在一个burst读没有完成的情况下输出下一个burst地址吗?也就是说,第二个图的两个burst地址会不会来自同一个master?还有,这种传输挂起有什么好处呢?AXI和Avalon在这一功能上的处理是完全一样的吗(从端口都支持burst读的传输挂起,主端口是不是都支持或者都不支持)?

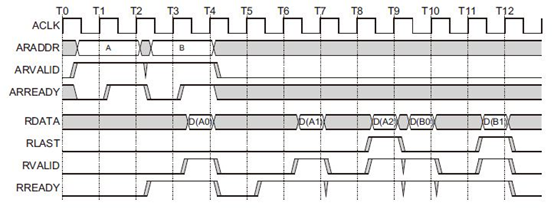

AXI读时序

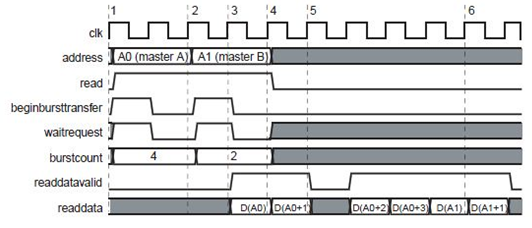

Avalon读时序(从端口)

从上面两个时序图都可以看出,两种总线都支持在一个burst未完成的情况下接收下一个burst地址,这里称之为传输挂起

Avalon总线协议里明确标出了这个时序图是从端口的时序,从图上可以看出,两个burst来自不同的master。AXI总线没有注明是从端口还是主端口。

我的疑问是,一个master的端口也会在一个burst读没有完成的情况下输出下一个burst地址吗?也就是说,第二个图的两个burst地址会不会来自同一个master?还有,这种传输挂起有什么好处呢?AXI和Avalon在这一功能上的处理是完全一样的吗(从端口都支持burst读的传输挂起,主端口是不是都支持或者都不支持)?

高手都在哪呢?

主和从是相对的。以读为例,AXI支持发出overlap的读操作,这意味着aximaster在当前发出的ar指令对应的rchannel 数据返回之前发出下一个AR命令,同理,axi slave收到一个ar指令后,在其返回对应r channel数据之前,其可以buffer下一个ar指令。

沙发。

还是有一定的道理的了

axi的spec里面的description那个chapter已经讲了时序图中端口的信号是属于master还是slave的,然后axi支持overlap操作,也就是在没有得到响应数据时,可以继续发下一个address。