RTL仿真通过了,但是门级仿真过不了,求大神帮助

时间:10-02

整理:3721RD

点击:

module keyfull_test(key,i,sensor,clk,rst_n,rx_data);

input[3:0] key;//决定触发器被何种信号触发(PC串口,按键,传感器)

input[3:0] sensor;//传感器信号入口

input rst_n;

input[7:0] rx_data;

input clk;

output[3:0] i;

reg[3:0] i;

wire[3:0] rx_data_l;

reg[15:0] state,nextstate;

assign rx_data_l=rx_data[3:0];

//assign rx_data_l=7;

parameter s0=4'b0,

KEYE=4'b0001,RS485E=4'b0010,

SENSORE=4'b0100,

FIRE=4'b1000;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

state<=s0; //复位

else

state<=nextstate;

end

always @(state or key)

begin

case(state)

s0:if(key==1)nextstate=KEYE;

else if(key==2)nextstate=RS485E;

else if(key==3)nextstate=SENSORE;

else nextstate=s0; //状态s0

KEYE:if(key==1)

nextstate=KEYE;

else if((key==4)||(key==5)||(key==6)||(key==7)||(key==8)||(key==9))

nextstate=FIRE;

else

nextstate=s0; //状态s4

RS485E:if(key==2)

nextstate=RS485E;

else

nextstate=s0; //状态s5

SENSORE:if(key==3)

nextstate=SENSORE;

else

nextstate=s0; //状态s6

FIRE:if((key==4)||(key==5)||(key==6)||(key==7)||(key==8)||(key==9)||(key==11)||(key==10))

nextstate=FIRE;

else

nextstate=s0;

default:state=s0;

endcase

end

always @(state or key or rst_n)

begin

if(!rst_n) begin

i=4'b0;

end

else begin

/* if (state == KEYE)

i=key-4'b0011;*/

if (state == RS485E)

i=rx_data_l;

else if (state == SENSORE)

i=sensor;

else if (state == FIRE)

i=key-4'b0011;

else begin

i=4'b0000;

end

end

end

endmodule

下面是testbench

`timescale 1 ps/ 1 ps

module keyfull_test_vlg_tst();

// constants

// general purpose registers

reg eachvec;

// test vector input registers

reg clk;

reg [3:0] key;

reg rst_n;

wire [7:0] rx_data;

wire [3:0] sensor;

// wires

wire [3:0] i;

assign sensor=4'b1010;

assign rx_data=8'b11001111;

// assign statements (if any)

keyfull_test i1 (

// port map - connection between master ports and signals/registers

.clk(clk),

.i(i),

.key(key),

.rst_n(rst_n),

.rx_data(rx_data),

.sensor(sensor)

);

initial

begin

clk=0;

rst_n=1;

#100 rst_n=0;

#500 rst_n=1;

#50 key=2;

#500000 key=3;

#500000 key=1;

#500000 key=6;

$display("Running testbench");

end

always

begin

@eachvec;

end

always

#10 clk=~clk;

endmodule

这个状态机应该来说没问题啊,怎么回事呢?

我刚刚把testbench 的时间单位改过来了,改成1ns/ps

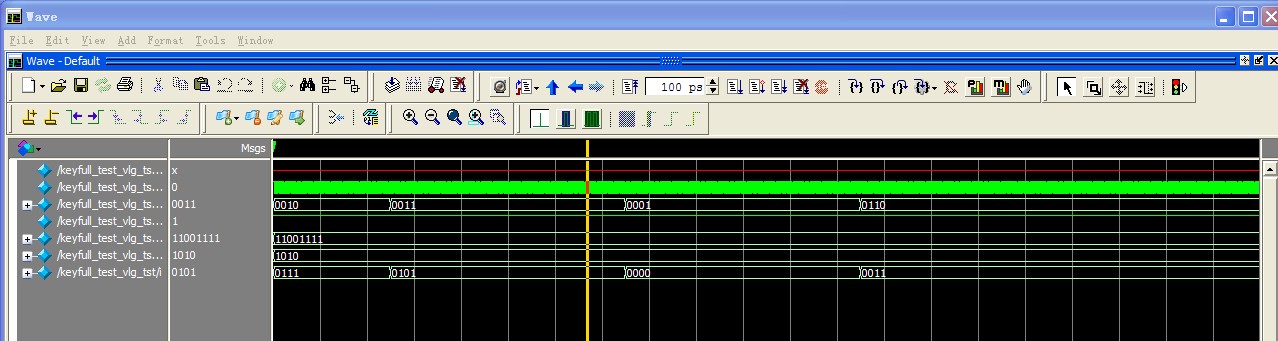

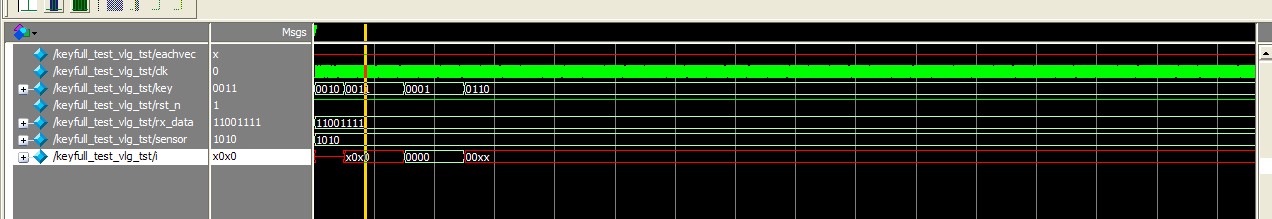

可是还是不行,仿真结果是这样的,时钟改为80ns时,仿真就通过了,结果是确定的,

,目前就是时钟小的时候,输出i就是确定的,时钟周期大的时候,只要输出i值中有1,就会变为x,不确定,0倒是可以正确输出,这到底是什么原因,那位大神点化一下,项目被堵了好几天了

,目前就是时钟小的时候,输出i就是确定的,时钟周期大的时候,只要输出i值中有1,就会变为x,不确定,0倒是可以正确输出,这到底是什么原因,那位大神点化一下,项目被堵了好几天了

input[3:0] key;//决定触发器被何种信号触发(PC串口,按键,传感器)

input[3:0] sensor;//传感器信号入口

input rst_n;

input[7:0] rx_data;

input clk;

output[3:0] i;

reg[3:0] i;

wire[3:0] rx_data_l;

reg[15:0] state,nextstate;

assign rx_data_l=rx_data[3:0];

//assign rx_data_l=7;

parameter s0=4'b0,

KEYE=4'b0001,RS485E=4'b0010,

SENSORE=4'b0100,

FIRE=4'b1000;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

state<=s0; //复位

else

state<=nextstate;

end

always @(state or key)

begin

case(state)

s0:if(key==1)nextstate=KEYE;

else if(key==2)nextstate=RS485E;

else if(key==3)nextstate=SENSORE;

else nextstate=s0; //状态s0

KEYE:if(key==1)

nextstate=KEYE;

else if((key==4)||(key==5)||(key==6)||(key==7)||(key==8)||(key==9))

nextstate=FIRE;

else

nextstate=s0; //状态s4

RS485E:if(key==2)

nextstate=RS485E;

else

nextstate=s0; //状态s5

SENSORE:if(key==3)

nextstate=SENSORE;

else

nextstate=s0; //状态s6

FIRE:if((key==4)||(key==5)||(key==6)||(key==7)||(key==8)||(key==9)||(key==11)||(key==10))

nextstate=FIRE;

else

nextstate=s0;

default:state=s0;

endcase

end

always @(state or key or rst_n)

begin

if(!rst_n) begin

i=4'b0;

end

else begin

/* if (state == KEYE)

i=key-4'b0011;*/

if (state == RS485E)

i=rx_data_l;

else if (state == SENSORE)

i=sensor;

else if (state == FIRE)

i=key-4'b0011;

else begin

i=4'b0000;

end

end

end

endmodule

下面是testbench

`timescale 1 ps/ 1 ps

module keyfull_test_vlg_tst();

// constants

// general purpose registers

reg eachvec;

// test vector input registers

reg clk;

reg [3:0] key;

reg rst_n;

wire [7:0] rx_data;

wire [3:0] sensor;

// wires

wire [3:0] i;

assign sensor=4'b1010;

assign rx_data=8'b11001111;

// assign statements (if any)

keyfull_test i1 (

// port map - connection between master ports and signals/registers

.clk(clk),

.i(i),

.key(key),

.rst_n(rst_n),

.rx_data(rx_data),

.sensor(sensor)

);

initial

begin

clk=0;

rst_n=1;

#100 rst_n=0;

#500 rst_n=1;

#50 key=2;

#500000 key=3;

#500000 key=1;

#500000 key=6;

$display("Running testbench");

end

always

begin

@eachvec;

end

always

#10 clk=~clk;

endmodule

这个状态机应该来说没问题啊,怎么回事呢?

always

#10 clk=~clk;

这个时钟太大了,20ps (50G) ==!

我刚刚把testbench 的时间单位改过来了,改成1ns/ps

可是还是不行,仿真结果是这样的,时钟改为80ns时,仿真就通过了,结果是确定的,

,目前就是时钟小的时候,输出i就是确定的,时钟周期大的时候,只要输出i值中有1,就会变为x,不确定,0倒是可以正确输出,这到底是什么原因,那位大神点化一下,项目被堵了好几天了

,目前就是时钟小的时候,输出i就是确定的,时钟周期大的时候,只要输出i值中有1,就会变为x,不确定,0倒是可以正确输出,这到底是什么原因,那位大神点化一下,项目被堵了好几天了

你有delay的概念吗?

首先请问下你综合net时设的clk周期是多少?你的testbench的时钟频率需要和综合时的吻合的,不是你想设10ns就10ns,80ns就80ns的。

其次,即使clk设对了,综合后的net,不反标sdf的话仿真时会加载库里默认的延迟值,有可能时序违例,就会出x。

如果还没做cts的话,最好是后仿时让仿真器不加载延迟、不判断时序违例。(在vcs里好像是-notiming_check -delay_mode_zero)。

如果已经做了cts就反标sdf。

也可以反标综合后的sdf,但意义不大。

没有,菜鸟一个啊

我看看,我从来没有想过综合net时clk还要设置,反标SDF,我都没有概念,cts不知道是什么,看来我得好好的查查了,谢谢ls,我来查查看,真的感谢你指点方向,否则太迷茫了,感激涕零。

路还很长啊

时钟频率不是无限大的,综合报告里有最大系统频率,

菜鸟来学习

if your clk's period is less than the setup time of the gate, is there a reasonable result?