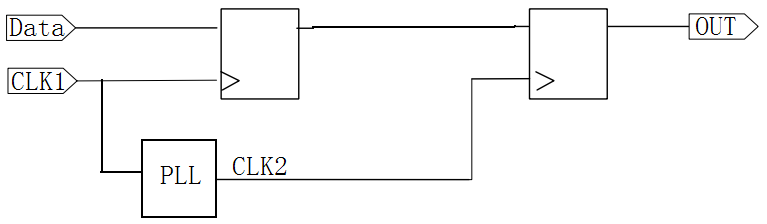

请问图中的两个时钟间要设置set_false_path吗?

时间:10-02

整理:3721RD

点击:

这两个时钟算是同步时钟还是异步时钟呀?用不用设set_false_path?

RTL中有跨时钟域特殊处理,就set_false_path。否则,就不用。

经过PLL之后就是异步时钟了。

没有跨时钟域,CLK1是50M,CLK2是倍频后的100M,将数据data倍频输出而已,我在DC中没有设置set_false_path,但是后端的setup违反很大呀,不知道和这有没有关系?

有一个简单的方法:

你拿100M寄存器寄存器二分频到50M再给逻辑用,将PLL输出端作为时钟源,就好处理多了。

您的意思是将PLL输出的100M作为原时钟,然后寄存器分频输出50M来处理信号,是吗?那这两个时钟间要设set_false_path吗?

对,不需要跨时钟域处理。其实原方案也可行,不过时序约束起来麻烦些。

请问一般用什么工具画这种电路图?

不用,这个时候这两个时钟是同步时钟,因为他们的之间的相位是固定的

分频输出后也应该算作跨时钟域了,个人觉得,只要没有严格同相位时钟,就应该算作跨时钟域。

就一般画图板就可以。

没有严格的同相位时钟,因为Skew总是存在的。

只要“相位差恒定”,就可以作为同时钟域,工具也可以正常计算。