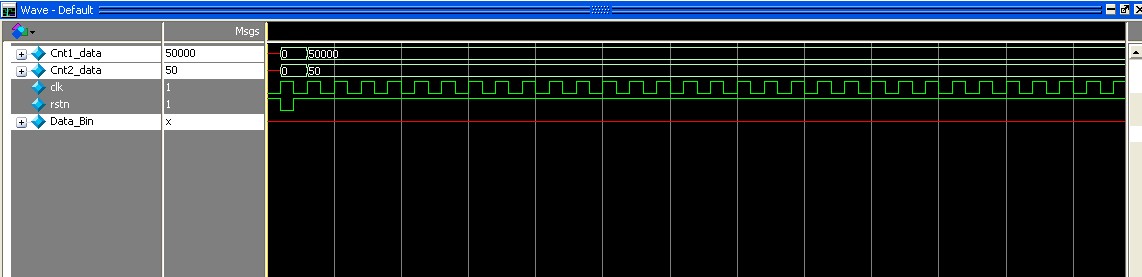

diveder模块的输出没有,是怎么回事?代码及仿真如下。

module divider

(

clk, rstn,

Cnt1_data,

Cnt2_data,

Data_Bin

);

input clk, rstn;

input [31:0]Cnt1_data;

input [31:0]Cnt2_data;

output [31:0]Data_Bin;

/***********************************************/

parameter Freq_50KHz = 16'd50_000; //Fs = Freq_50KHz

/***********************************************/

reg [31:0]Cnt1_in, Cnt2_in; //Ns = Cnt1_in, Nx = Cnt2_in

reg [31:0]Data_out; //Fx = Data_out

reg div_over;

always @ ( posedge clk or negedge rstn )

if( !rstn )

begin

Cnt1_in <= 32'd0;

Cnt2_in <= 32'd0;

div_over <= 1'd0;

end

else if( ( Cnt2_in >= Cnt1_in ) && ( div_over == 0 ) )

begin

Cnt2_in <= Cnt2_in - Cnt1_in;

Data_out <= Data_out + 1'b1;

end

else if( Cnt2_in < Cnt1_in )

begin

div_over <= 1'd1;

end

else

begin

Cnt1_in <= Cnt1_data;

Cnt2_in <= Cnt2_data * Freq_50KHz;

end

/***********************************************/

assign Data_Bin = Data_out;

/***********************************************/

endmodule

testbench写的应该没问题,不过也贴出来。

testbench代码如下:

`timescale 1 ns/ 1 ns

module divider_vlg_tst();

reg [31:0]Cnt1_data;

reg [31:0]Cnt2_data;

reg clk;

reg rstn;

wire [31:0]Data_Bin;

/*****************************/

divider i1

(

.Cnt1_data(Cnt1_data),

.Cnt2_data(Cnt2_data),

.Data_Bin(Data_Bin),

.clk(clk),

.rstn(rstn)

);

/*****************************/

initial

begin

clk = 0;

rstn = 1;

#10 rstn = 0;

#10 rstn = 1;

end

always #10 clk = ~clk;

/**************************************/

always @ ( posedge clk or negedge rstn )

if( !rstn )

begin

Cnt1_data <= 32'd0;

Cnt2_data <= 32'd0;

end

else

begin

Cnt1_data <= 32'd50_000;

Cnt2_data <= 32'd50;

end

/**************************************/

endmodule

大家帮忙分析分析,谢了~!

高手们,看看吧!

Cnt2_in <= Cnt2_data * Freq_50KHz;

这样写行吗?

这个always块永远进下面这个分支。

else if( ( Cnt2_in >= Cnt1_in ) && ( div_over == 0 ) )

begin

Cnt2_in <= Cnt2_in - Cnt1_in;

Data_out <= Data_out + 1'b1

分频,你先把分频的值load进去

谢了哈!

改成下面代码之后还是不行啊

/***********************************************/

reg [31:0]Cnt1_in, Cnt2_in; //Ns = Cnt1_in, Nx = Cnt2_in

reg [31:0]Data_out; //Fx = Data_out

reg init_flag = 1'd0;

reg div_over = 1'd0;

always @ ( posedge clk or negedge rstn )

if( !rstn )

begin

Cnt1_in <= 32'd0;

Cnt2_in <= 32'd0;

Data_out <= 32'd0;

div_over <= 1'd0;

init_flag <= 1'd0;

end

else if( !init_flag )

begin

init_flag <= 1'd1;

Cnt1_in <= Cnt1_data;

Cnt2_in <= Cnt2_data * Freq_50KHz;

end

else if( ( Cnt2_in >= Cnt1_in ) && ( !div_over ) && ( init_flag ) )

begin

Cnt2_in <= Cnt2_in - Cnt1_in;

Data_out <= Data_out + 1'b1;

end

else if( Cnt2_in < Cnt1_in )

begin

div_over <= 1'd1;

end

/***********************************************/

有数据,但是data_out不停的往上加,我要的是加到50就停的!