Modelsim 仿真时,输入信号出现如下情况,是怎么回事?

testbench如下:

`timescale 1 ns/ 1 ns

module BintoBCD_vlg_tst();

reg clk;

reg [7:0] bin_in;

wire [3:0]dec_out0;

wire [3:0]dec_out1;

wire [3:0]dec_out2;

/****************************/

initial

begin

clk = 0;

bin_in = 8'd125;

end

always #10 clk = ~clk;

/****************************/

/* always @ ( posedge clk )

if( load )

begin

bin_in = 8'd0;

end

else

begin

bin_in = 8'd125;

end

*/

/****************************/

endmodule

模块如下:

module BintoBCD

(

input clk,

input[7:0] bin_in, //输入8bit Bin码

output reg[3:0]dec_out0 = 4'h0, //输出3bit BCD码

output reg[3:0]dec_out1 = 4'h0,

output reg[3:0]dec_out2 = 4'h0

);

/***********************************************/

wire [2:0]c_in;

wire [2:0]c_out;

reg [7:0]bin_sreg;

reg [3:0]bit_cnt = 4'h0;

reg [3:0]dec_sreg0 = 4'h0;

reg [3:0]dec_sreg1 = 4'h0;

reg [3:0]dec_sreg2 = 4'h0;

wire [3:0]next_sreg0, next_sreg1, next_sreg2;

wire load = ~|bit_cnt; //读入二进制数据,准备转换

wire convert_ready = ( bit_cnt == 4'h9 ); //转换成功

wire convert_end = ( bit_cnt == 4'ha ); //完毕,重新开始

/***********************************************/

always @ ( posedge clk )

begin

if( convert_end )

bit_cnt <= 4'h0;

else

bit_cnt <= bit_cnt+4'h1;

end

/***********************************************/

always @ ( posedge clk )

begin

if( load )

bin_sreg <= bin_in;

else

bin_sreg <= { bin_sreg[6:0], 1'b0 };

end

/***********************************************/

assign c_in[0] = bin_sreg[7];

assign c_in[1] = ( dec_sreg0 >= 5 );

assign c_in[2] = ( dec_sreg1 >= 5 );

assign c_out[0] = c_in[1];

assign c_out[1] = c_in[2];

assign c_out[2] = ( dec_sreg2 >= 5 );

/******************确定移位输出******************/

assign next_sreg0 = c_out[0] ? ( { dec_sreg0[2:0], c_in[0] } + 4'h6 )

: ( { dec_sreg0[2:0], c_in[0] } );

assign next_sreg1 = c_out[1] ? ( { dec_sreg1[2:0], c_in[1] } + 4'h6 )

: ( { dec_sreg1[2:0], c_in[1] } );

assign next_sreg2 = c_out[2] ? ( { dec_sreg2[2:0], c_in[2] } + 4'h6 )

: ( { dec_sreg2[2:0], c_in[2] } );

/*******************装入数据********************/

always @ (posedge clk )

if( load )

begin

dec_sreg0 <= 4'h0;

dec_sreg1 <= 4'h0;

dec_sreg2 <= 4'h0;

end

else

begin

dec_sreg0 <= next_sreg0;

dec_sreg1 <= next_sreg1;

dec_sreg2 <= next_sreg2;

end

/*********************数据输出******************/

always @ ( posedge clk )

if( convert_ready )

begin

dec_out0 <= dec_sreg0;

dec_out1 <= dec_sreg1;

dec_out2 <= dec_sreg2;

end

/***********************************************/

endmodule

顶起!~

你没有例化RTL模块

/****************************/

BintoBCD i1

(

.clk( clk ),

.bin_in( bin_in ),

.dec_out0( dec_out0 ),

.dec_out1( dec_out1 ),

.dec_out2( dec_out2 )

);

/***********************************************/

这个在发帖子的时候不小心删了,谢谢提醒。在testbench文件里面是有的。

还是出现上述情况。

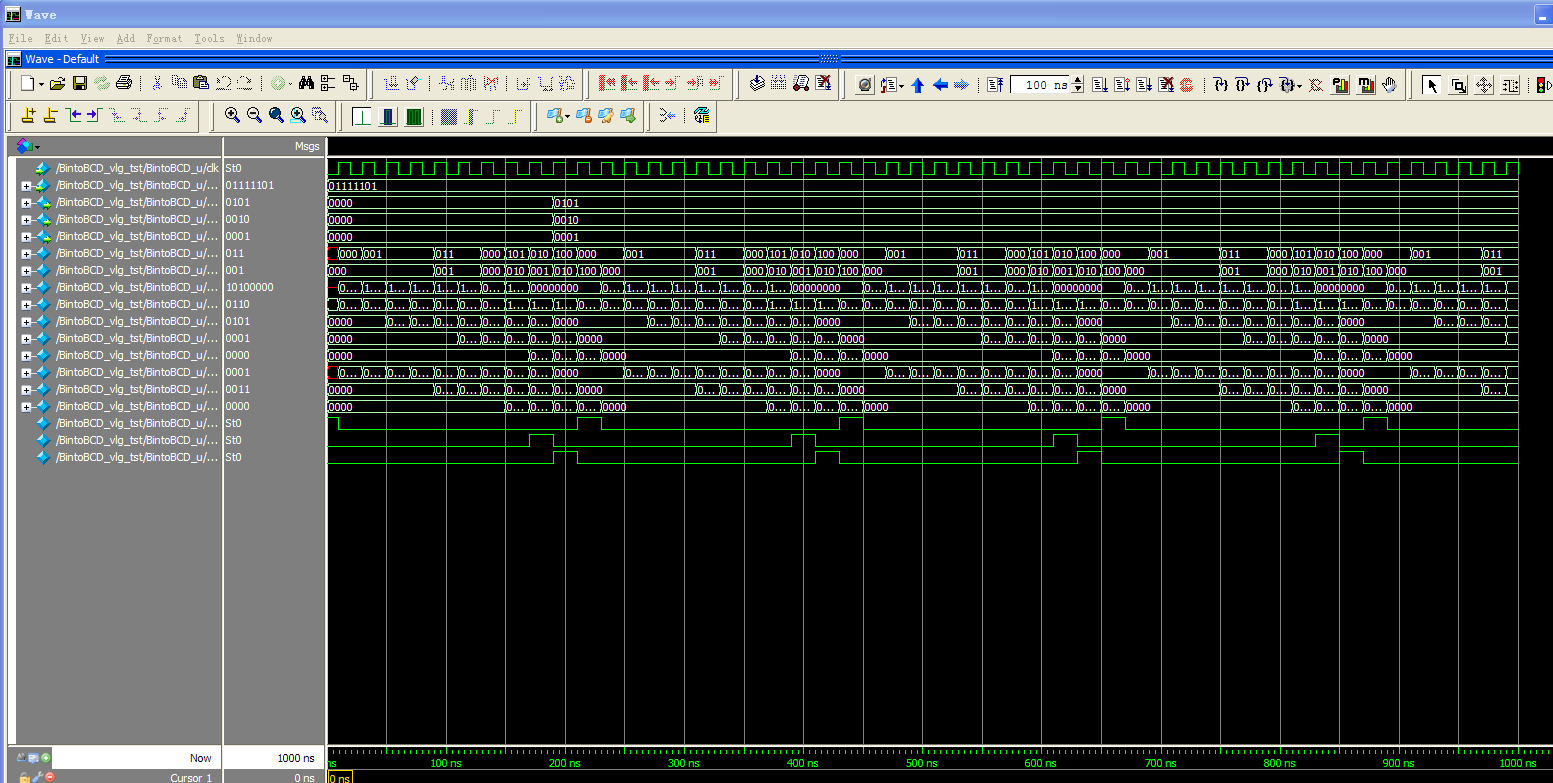

你的信号没有进去,这是我在你testbench添加的

BintoBCD BintoBCD_u (.clk(clk),.bin_in(bin_in),.dec_out0(dec_out0),.dec_out1(dec_out1),.dec_out2(dec_out2));

就这一个改动,其他都是你的代码,波形出来了,如图

不胜感激!

估计是我的软件问题!

终于解决了!工程建的有问题,把以前的全部删掉,重新建一次就行了@!

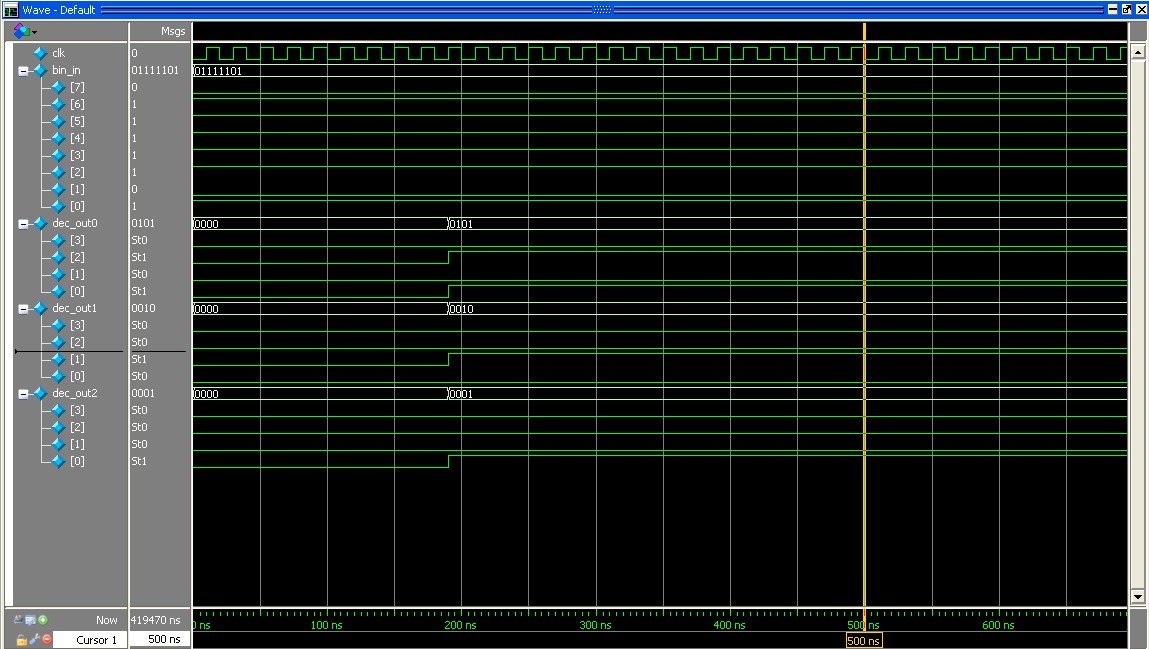

输入的是125的二进制,

dec_out2为 0001------1

dec_out1为 0010------2

dec_out0为 0101------5

顶起oooooooo