求助,对RGMII网络芯片的输入输出进行io约束

时间:10-02

整理:3721RD

点击:

最近在做千兆网的时序通信,数据手册是英文的,看得头大,然后在做时序约束的时候总是不能达到理想的效果,请教各位高手帮忙看看。

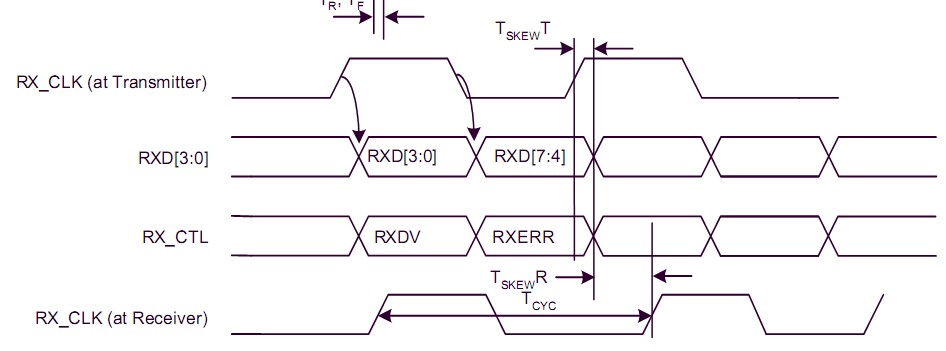

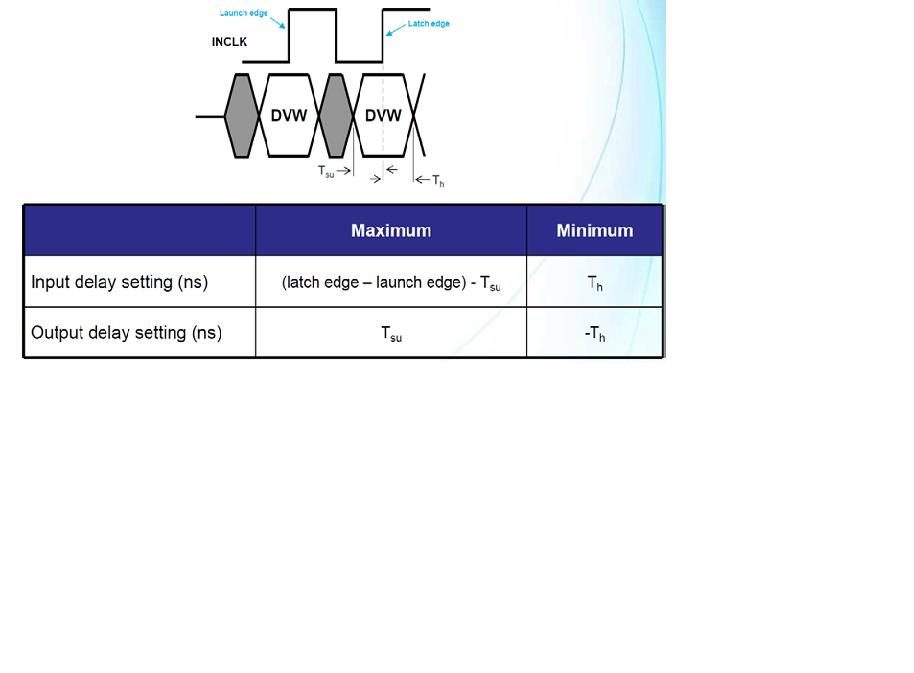

使用RGMII协议,quartus里的ddio模块直接和网络芯片连接。然后网络芯片的Tsu和Th根据时序图和表格算出来的,Tsu=1-0.7/2=0.625ns Th=4-(2.6+0.7/2)=1.025

时钟是125MHz,数据输入输出都是同源的,时钟线和数据线差不多等长,忽略下,同源的时钟约束按照表里的公式做的

input_max=4-0.625=3.375 input_min=1.025 out_max=0.625 out_min=-1.025,写好约束,并且在timequest里约束通过。这样的约束在班上调试的时候并不能达到稳定效果,希望各位高手能够指导下,那边出了错。

上ALTERA网站,专门有个PDF文档介绍关于RGM约束的,在实际应用中没有任何问题

布线后tclk,txd之间tco相差最大有几NS

我是我还是有点搞不清我算的Tsu和Th对不对,还有用的FPGA已经没有PLL资源了,不知有没有影响

rgmii不消耗PLL,与那个无关,主要看input_delay和output_delay的设置,你抓avalon侧的波形看看,看看收到的数据对不对,你是使用的例化IP CORE时生成的那个SDC文件吧

谢谢你的回答,在Altera网站找到一篇pdf:Designing RGMII Interfaces with FPGAs and HardCopy ASICs 不知道你说的是不是这个,

看pdf的一个疑问,将输出setup的多路径设为0,时间肯定是不够的啊。

没有使用avalon,只例化了使用的ddio,sdc是自己写的

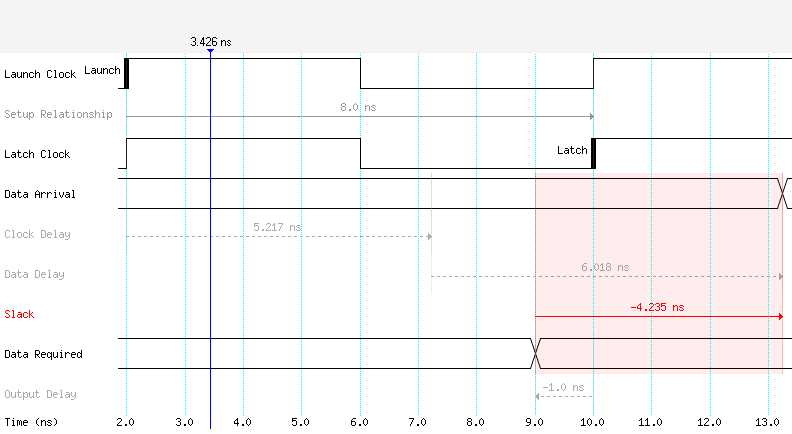

今天参照altera的PDF将网络芯片设置为延时,输入约束之后可以可以收到数据,然后输出的数据不太对,我是在另一个FPGA里抓的数据,这片时做好的。

这是输出最差的时序图

我知道问题大概是在时序约束上,我却不是很了解明白这个,约束起来很困难