关于几个器件的延时(sdc文件)

时间:10-02

整理:3721RD

点击:

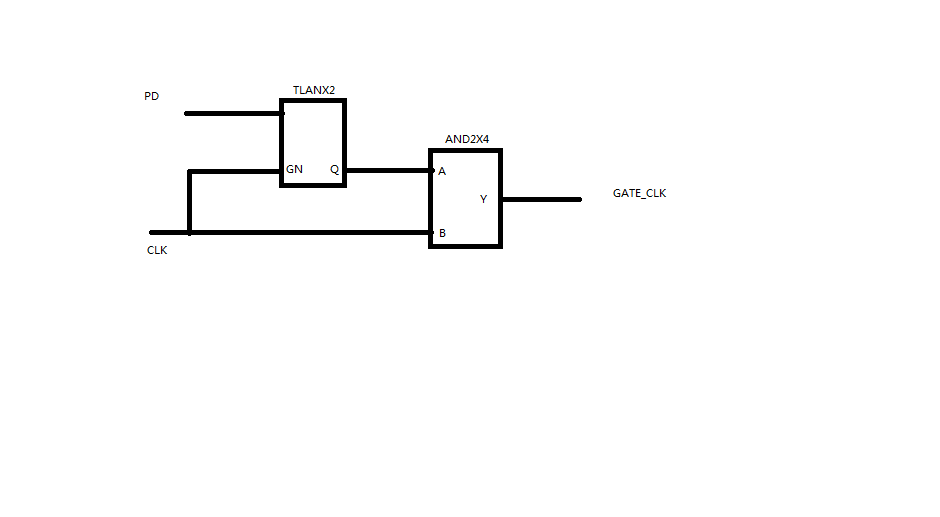

刚开始接触数字前端的时序的东西,有一个问题请教。先看电路图:

然后问题是从CLK到GATE_CLK的延时是多少?

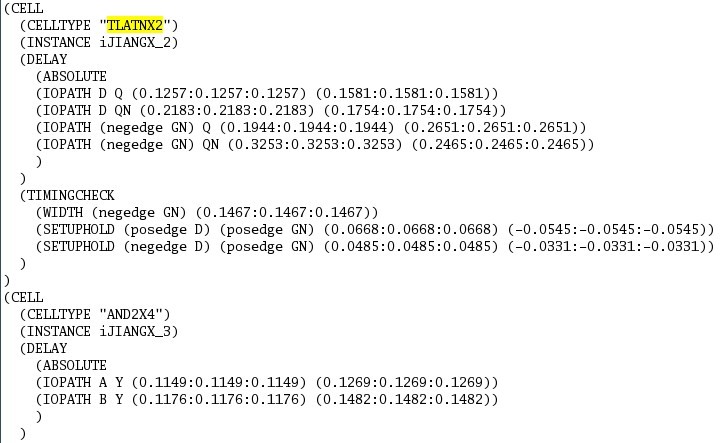

下面是sdc文件:

其中最主要的几个参数是GN---Q(0.1994)(0.2651)和A--Y(0.1149)(0.1269)

我是这样想的,因为是一个始终信号,肯定基友上升沿,又有下降沿,然后迷糊了到底用哪几个数据相加得到所要的延时?

你这是SDF,好吧

这东西是反标注到 std verilog 的specify block里定义的module path上的,这里定义的module path与timing check与specify block里定义的是一致的,反标注后,sdf里的延时代替specify block里定义的1ns

sdf在仿真和sta的时候会自动标注;

你关心的问题,设计工具的人已经有考虑了。

时须分析工具会自己计算在输入信号的哪种变化(0->1 / 1->0)下,整条path的delay 最大。所以你仔细看DC/PT的时须报告,一般都会告诉你:某个具体的cell在计算整条path delay的时候,使用的是这个cell 的rising delay or falling delay.

谢谢楼上,那么我们自己估计的话,是不是按最大的来算,再加上点裕量?