FPGA实现FIR滤波器

时间:10-02

整理:3721RD

点击:

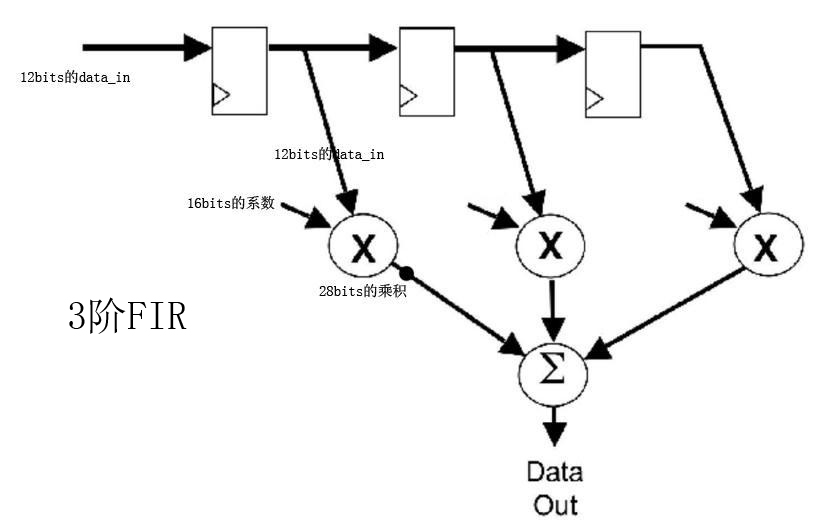

请教大家个问题,FPGA实现滤波器,系数都是先经过matlab计算,然后乘以2^N之后得到的。

像附图,16bit的系数也是,那么,最后计算结束后必须除以2^N(截位或者舍入),

但是在哪里除比较好呢?

是在乘法器输出那里,还是在最后加法器输出那里呢?

要是在乘法器那里就除的话,误差会非常大;如果在最后加法器输出那里除,那么这个加法器

位宽将会非常大,很耗资源,能跑的速度不高,当然也可以用流水线,但是,太耗资源,不知道

大家平时都是怎么实现的呢?

看了好一会才明白说的就是系数小数点的处理问题,你用的是什么器件?

才28BIT位宽,没问题的,这速度跑一二百M都应可以,在乘法器里适应选择上CORE内部寄存器,不行在CORE外再来个寄存器,加法时PIPE一下,这都容易实现。

至于资源,这点资源没多少,系数才16位,会调用18*18的DSP,

一般是在最后截位

阶数很大的话呢,一般来说,DDC、DUC的整形滤波器阶数都很大,这样资源消耗就多了,而且那么大位宽的加法器,速度比较难保证,

好在整形滤波器都在采样率最低的时候

xue xie le

滤波器,好久以前的事了! 忘得差不多了

这个问题。看你的精度要求。一般是两级截位。 乘法出来截位一次,加法出来截位一次。 你的信号位宽才12bit,滤波器系数也才用16bit,精度应该不会很高,这种情况,放心大胆的在乘法其后面处理吧。

乘法器是最低也位宽也是18x18,乘法输入18bit以内都不会影响资源。这时候你的系数和信号都不足18bit。可见精度要求并不高了。

如果信号和系数都扩展成18bit,在乘法后面取成你现在的28bit,精度也比现在高不少。