初学者,写的增量式pi控制器,哪位大神有空能不能帮忙给看看,谢谢!

时间:10-02

整理:3721RD

点击:

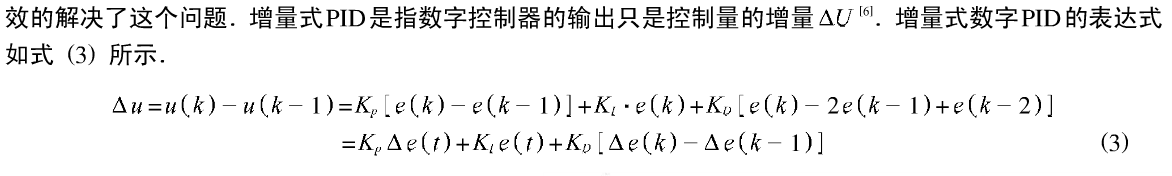

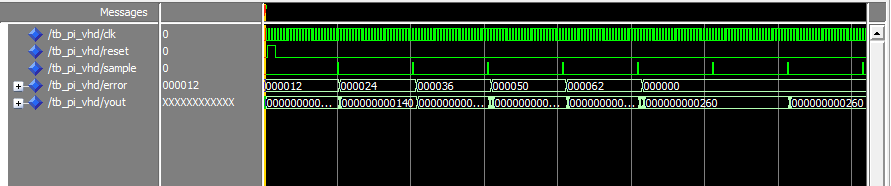

就是根据这个式子写的,其中e(t)是误差,其中没有计算微分,只计算了,比例跟积分,Post & Route Simulation,behavioral simulation和post-translate simulation都过了,但post-map simulation没有过,出现都是红色的线,不知道下载后能不能正常运行。

entity pi is

Port ( clk : in STD_LOGIC;

reset:in std_logic;

sample : in STD_LOGIC;

error : in STD_LOGIC_VECTOR (17 downto 0);

yout : out STD_LOGIC_VECTOR (35 downto 0));

end pi;

architecture Behavioral of pi is

signal kp:std_logic_vector (17 downto 0);

signal ki:std_logic_vector (17 downto 0);

signal old:std_logic_vector (17 downto 0);

signal dif:std_logic_vector (17 downto 0);

signal p1:std_logic_vector (35 downto 0);

signal p2:std_logic_vector (35 downto 0);

signal y:std_logic_vector (35 downto 0);

signal oldy:std_logic_vector (35 downto 0);

component my_mutl port(

A:IN STD_LOGIC_VECTOR(17 DOWNTO 0);

B:IN STD_LOGIC_VECTOR(17 DOWNTO 0);

P:OUT STD_LOGIC_VECTOR(35 DOWNTO 0));

END COMPONENT;-------ip核定制的乘法器

begin

process(clk,reset)

begin

if reset='1' then

kp<="000000000000000010";

ki<="000000000000000010";

old<="000000000000000010";

oldy<=(others=>'0');

elsif clk'event and clk='1' then

if sample='1' then

old<=error;

oldy<=y;

end if;

end if ;

end process;

dif<=error-old;----------------------------old为上个采样周期的error的值,dif为本次误差与上次采样时误差的差值

mutl1:my_mutl port map(dif,kp,p1);

mutl2:my_mutl port map(ki,error,p2);

y<=oldy+p1+p2;--------------------------oldy为上次采样时的控制器输出值

yout<=y;

end Behavioral;

下面是post-translate simulation的一个仿真图

哪位大神帮忙给指点下,看正确吗,因为对这方面不是很了解,十分感谢!