初学者——关于异或门毛刺的问题

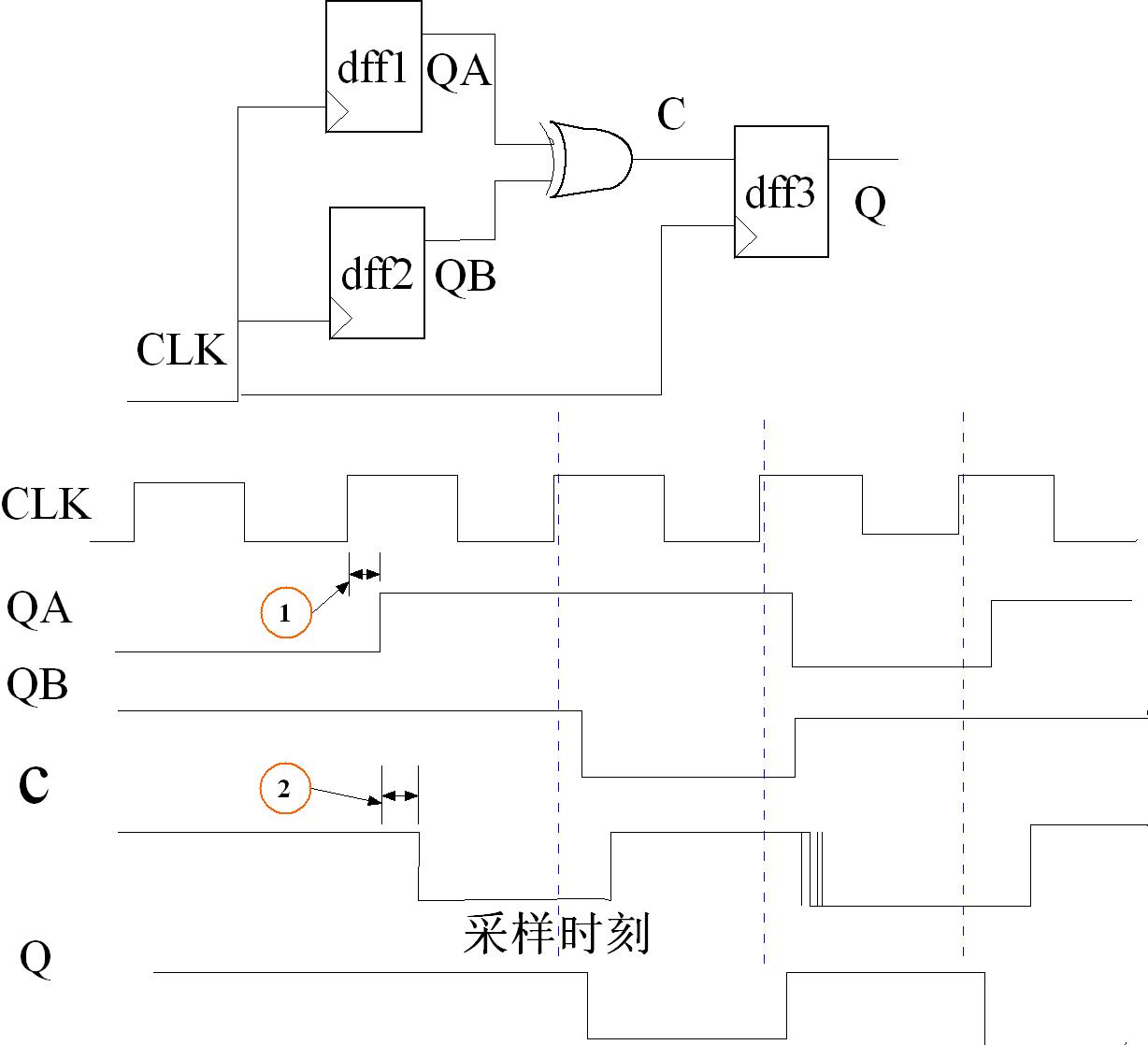

例如,时钟控制的两个输入通过异或门后结果再被触发器锁存,锁存器的时钟同输入的时钟。

2、对上面例子中的情况异或门产生的毛刺应该采取什么办法清除?

3、我用的是modelsim5.8 se 在仿真时好像考虑了器件的延迟,在仿真时有命令可以修改参数不考虑延迟吗?

请大家给予帮助,先谢谢大家先!

建议你先看一些时序方面的资料,一般来说setup和holdup满足了的话,是不会采到毛刺或出现亚稳态的。我只见到过在异步设计中才考虑亚稳态。

如图所示,由于寄存器和xor有门延迟,信号在线上走的时候也会有传输延迟,图中标号1表示寄存器dff的输出延迟,标号2表示xor的门延迟。由于这些延迟的存在,dff3在采样c的时候不会采到毛刺或不稳定状态。当然如果极限地提高时钟频率,使时钟周期小于各种延迟加上dff的建立时间和的话,采样就会采到不稳定状态。

你可以用sta工具在加了合适的约束后检查时序条件是否都满足,也可以用后仿真来检查综合出的电路在映射布局布位后的波形是否正确,来判断你的设计时序究竟有没有出问题。

其实同步设计很难有机会时钟采样到毛刺,而且毛刺即便被采样到也不会满足setup和hold时间,所以不用担心

谢谢小编和apex回答我的问题。还有第三个问题啊!

我还是想问,小编的例子里面异或门的输入是触发器输出的两个信号,这两个信号同时到达的,但是假如现在是两级异或门组成的三输入的逻辑电路。首先是两个异或一下,结果再和另一个输入异或,前两个输入的异或结果和最后一个输入要有时间差的,这样就使得最终结果产生毛刺,由于输入都是时钟同步输入,这样这个毛刺在时钟的边沿处,宽度和时间差有关。宽度很小的话不就使得后面的寄存器的hold时间不足了吗?

我只是这么理解的,我在想难道没过一个异或门就要插入一级寄存器隔离一下吗,那样的话就太麻烦了。

请大家多多发言,给予指点。

你仔细看看什么叫hold timing。

hold timing检查,要保证上一级寄存器的输出信号,即使传播的再快,也不会被下一级寄存器采到。

这里面就包括了毛刺!

谢谢,我好像明白了一点!

那对于异或门即使信号同时到达,两个输入同时有变化的时候仍然有毛刺产生。

还有关于modelsim 5.8 se的延迟命令,各位多多帮忙,那英文的Manul太难懂了,

谢谢!

fdsfds

thanks a lot,,I encounted such problems

谢谢讲解,我好象有点明白了

共同受益哈

ding

3xs

只要时间足够长,就不会有毛刺或亚稳态吧。这个要看你的设计频率和实际电路延时的。

你如果真的担心毛刺造成的影响的话,可以在做电路版图的时候添加一些电容来避免吧?其实我觉得只要你的设计是满足设计规范的时序要求的话就不用担心这个问题的啊!

共同受益哈

仔细学习!仔细思考!

vsim +notimingcheck

小编想得比较深入啊,赞

学习了!