QUARTUS下RAM问题

时间:10-02

整理:3721RD

点击:

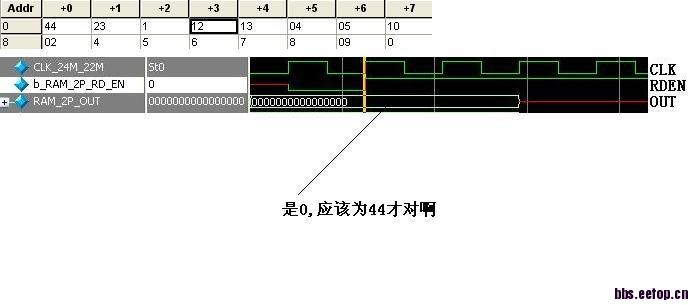

我用的IP, 2PORT-RAM

MIF文件里,初始化了所有地址的数据.

但数据读出来却是0

MIF文件里,初始化了所有地址的数据.

但数据读出来却是0

围观

你的波形中的信号是testbench中的还是ROM的输出?

时钟和读使能,是输给RAM的.

OUT,是RAM输出的数据.

RAM的0地址我初始化为44,但读出来始终是0

RAM用的是cyclone III内部M9K做的,直接用的IP MEGA里的2-port RAM核

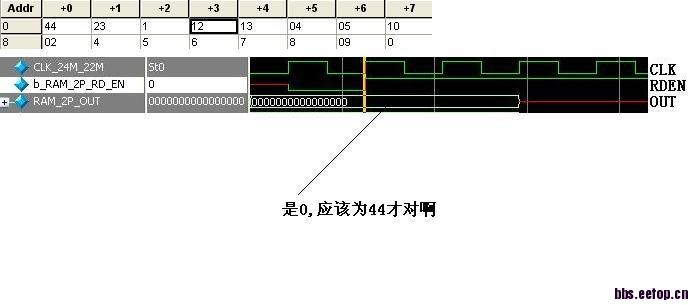

1.读信号使能后几个周期端口会送出数据?

2.第4个clk起来后你的信号是红线,是U还是X?

后面是XXXXXXXXXXX

不知道为什么