计数计数模块设计遇到的问题

用状态机控制吧

用状态机控制吧

能具体点吗?状态机我不是很熟

程序是

entity count is

port(

clk,start,stop,reset : in std_logic;

cout : out std_logic_vector(7 downto 0)

);

end count;

architecture behav of count

begin

process(clk,start,stop,reset)

variable c : std_logic_vector(7 downto 0);

begin

if reset='1' then

c:="00000000";

if clk'event and clk='1' then

if start'event and start='1' then

c:=c+1

elsif stop'event and stop='1' then

cout<=c;

end if;

end if;

cout<=c;

end process;

end behav

编译后出现错误:can't infer register for "c[0]" at count.vhd,because it does not hold its value outside the clock edge

非常谢谢

非常感谢

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity count is

port(

clk:in std_logic;

reset : in std_logic;

start: in std_logic;

stop: in std_logic;

cout : out std_logic_vector(7 downto 0)

);

end count;

architecture behav of count is

begin

process(clk,reset)

variable c : std_logic_vector(7 downto 0);

begin

if reset='1' then

c:="00000000";

cout<="00000000";

elsif clk'event and clk='1' then

if start='1' then

c:=c+1;

elsif stop='1' then

cout<=c;

end if;

end if;

end process;

end behav;

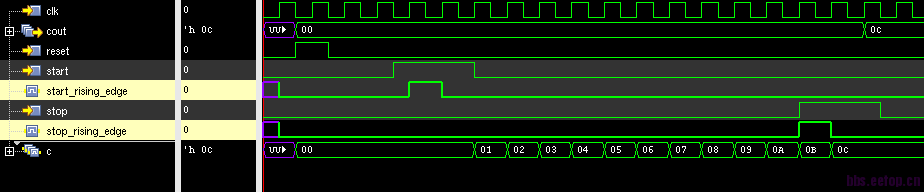

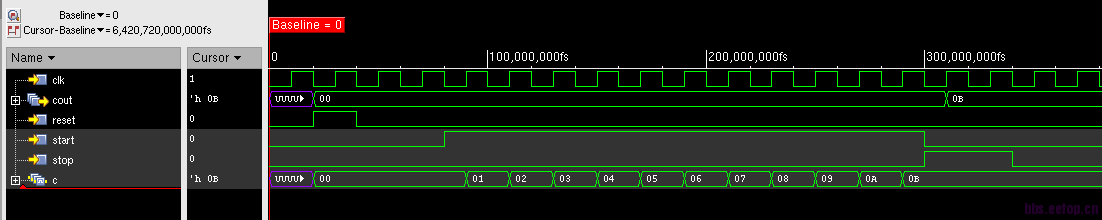

我做的是一个激光测距仪,用CPLD作时间间隔测量,就是测量激光从发射出去到碰到目标反射回来的时间,start是一PWM信号,作启动计数器的开门信号.stop就是回波信号,作关闭计数器的关门信号,我的思路是检测start信号的第一个上升沿作开门信号,stop的第一个上升沿作关门信号

我在Quartus II 里面建波形文件怎么仿真不出来呢?

那你需要先取start和stop的上升沿。

因为逻辑简单,就根据start和stop的上升沿产生计数的状态(cnt_status)。复杂时用状态机。

QuartusII不能仿真的原因不是很清楚,应该是软件没设置好,建议再看看帮助文档。我这里没有QuartusII所以没法给你截图。

下面是参考代码。

- library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_unsigned.all;

- entity count is

- port(

- clk:in std_logic;

- reset : in std_logic;

- start: in std_logic;

- stop: in std_logic;

- cout : out std_logic_vector(7 downto 0)

- );

- end count;

- architecture behav of count is

- signal start_dly1 : std_logic;

- signal start_dly2 : std_logic;

- signal start_rising_edge : std_logic;

- signal stop_dly1 : std_logic;

- signal stop_dly2 : std_logic;

- signal stop_rising_edge : std_logic;

- signal cnt_status : std_logic;

- begin

- process(clk,reset)

- begin

- if reset='1' then

- start_dly1 <= '0';

- start_dly2 <= '0';

- elsif clk'event and clk='1' then

- start_dly1 <= start;

- start_dly2 <= start_dly1;

- end if;

- end process;

- start_rising_edge <= not(start_dly2) and start_dly1;

- process(clk,reset)

- begin

- if reset='1' then

- stop_dly1 <= '0';

- stop_dly2 <= '0';

- elsif clk'event and clk='1' then

- stop_dly1 <= stop;

- stop_dly2 <= stop_dly1;

- end if;

- end process;

- stop_rising_edge <= not(stop_dly2) and stop_dly1;

- -- status

- process(clk,reset)

- begin

- if reset='1' then

- cnt_status <= '0';

- elsif clk'event and clk='1' then

- if start_rising_edge = '1' then

- cnt_status <= '1';

- elsif stop_rising_edge = '1' then

- cnt_status <= '0';

- end if;

- end if;

- end process;

- process(clk,reset)

- variable c : std_logic_vector(7 downto 0);

- begin

- if reset='1' then

- c:="00000000";

- cout<="00000000";

- elsif clk'event and clk='1' then

- if cnt_status = '1' then

- c:=c+1;

- else

- cout<=c;

- end if;

- end if;

- end process;

- end behav;