请问什么时候用两级flip-flop

两级FF的必要性从数字逻辑上是看不出来的。这种措施是为了防止初级寄存器在setup/hold不满足时输出非稳态0/1的结果,而这个结果通过不止一条路径被采样,最终这些采样结果即便在同一个时钟沿,值也不同,使得原有的逻辑关系被破坏。

试想,假定对内部DFF,在时钟上升沿时刻,当D端<1.0V时输出0,D端>1.2V时输出1,则必然存在一个1.0V~1.2V之间的某个值,使得输出非0且非1------因为这个世界是模拟的。这就是“亚稳态”。

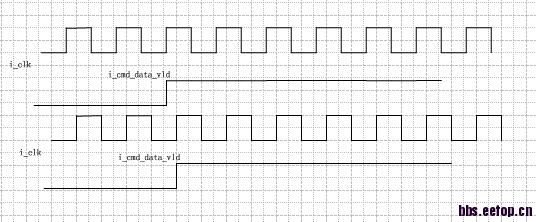

不妨设上面这个输出在这一拍先冲高到接近1再回落到接近0,且此输出驱动了2个DFF,而到这两个DFF的延时不同。这样的话就有可能延时小的DFF在下一拍采到0,而延时大的DFF采到1。这样逻辑关系就被破坏了,因为我们的数字逻辑是基于“同一拍采同一个输入得到同一个输出”的假设的。

当然,即便用两级DFF也有可能连续两次击中亚稳态,这个我们就要算一下概率了。通常几十兆频率下连续两次击中亚稳态的概率大概是几十年一次(MTBF),所以如果频率特别高的话也可以考虑用三级DFF。

这样说来,我如果只有一条支路采样,就不需要考虑亚稳态的问题啦?因为你上面提到的是多条支路采到的结果可能不同。

为了明确你的问题,我这样写出来。

数据传播路径: DFF1(原时钟域) -> DFF2(采样时钟域) -> DFF3(采样时钟域)

如果DFF2的下级寄存器只有一个(DFF3),那就不用单独考虑打两拍,因为其实这样跟打两拍没有区别。

如果DFF2驱动了2个以上的寄存器,那就不行。

非常感谢,我就想得到这句话,“DFF2驱动2个以上的寄存器”

每个CMOS的门都有一定的放大能力,多级可以将不定态信号推到一个确定的状态