基于APB协议的外设设计问题

时间:10-02

整理:3721RD

点击:

在MCS-51单片机中,串口相当于外设,CPU向外界发送数据时,先往串口缓冲写入数据,串口往外发送完后,产生中断请求,CPU才送下一个数据到串口缓冲;接收也类似。

考虑这样一个系统,由CPU、AHB、AHB到APB的桥接器、APB、低速外设(如RS232、I2C等)组成。

问题就是,如果CPU在AHB上执行一个很长的突发写传输,每一个时钟周期都送出一个数据,通过桥接器到挂在APB上的低速外设RS232,而RS232向外界发送的速度明显没有APB写入RS232缓冲区的速度快,从而导致RS232缓冲区一直塞满数据。这种情况下应该怎么处理?是不是对低速外设,就不应该发起一个很长的突发传输,而是应该向MCS-51那样,前一个处理完后中断请求再发送后一个数据?

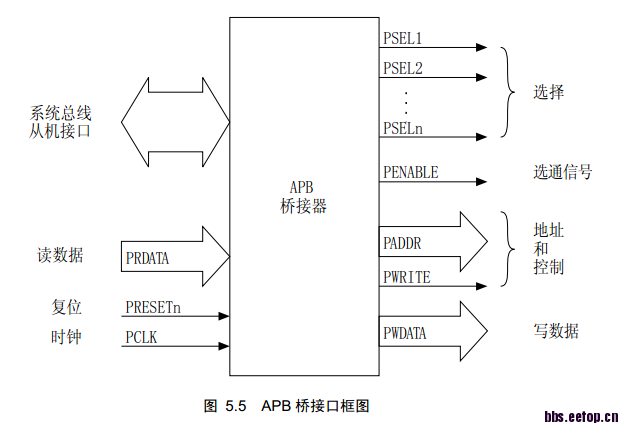

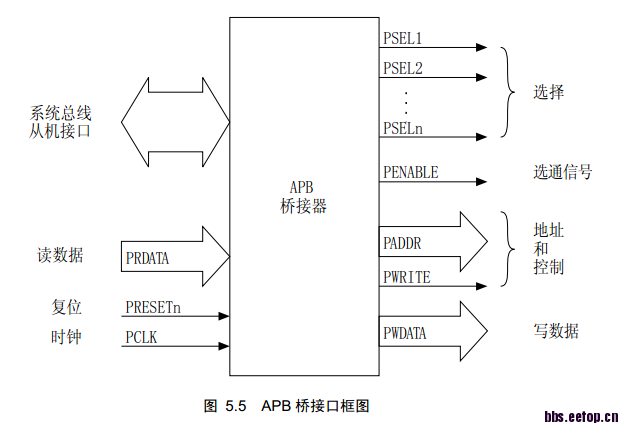

另外,注意到AMBA协议中,APB总线上的从机只产生数据输出到APB总线,而没有状态反馈之类的信号到APB总线,如下图所示。那么外设任务完成产生的中断信号,是不是不通过APB总线,而是单独接回给CPU?

望高人解答!

考虑这样一个系统,由CPU、AHB、AHB到APB的桥接器、APB、低速外设(如RS232、I2C等)组成。

问题就是,如果CPU在AHB上执行一个很长的突发写传输,每一个时钟周期都送出一个数据,通过桥接器到挂在APB上的低速外设RS232,而RS232向外界发送的速度明显没有APB写入RS232缓冲区的速度快,从而导致RS232缓冲区一直塞满数据。这种情况下应该怎么处理?是不是对低速外设,就不应该发起一个很长的突发传输,而是应该向MCS-51那样,前一个处理完后中断请求再发送后一个数据?

另外,注意到AMBA协议中,APB总线上的从机只产生数据输出到APB总线,而没有状态反馈之类的信号到APB总线,如下图所示。那么外设任务完成产生的中断信号,是不是不通过APB总线,而是单独接回给CPU?

望高人解答!

设buffer(fifo)

直接接irq给cpu

反压!~

CPU要访问外设,一般是先配置外设的寄存器,然后在启动发送/接收任务,再通过中断/查询监测任务是否完成。那么CPU配置外设的数据通过APB写入外设后,外设是不是应该有一个ACK信号返回给CPU?这个ACK信号和任务完成后的IRQ信号都是单独接回CPU吗?PS:AMBA总线只是数据和地址总线,并不包括控制信号,对不对?

AMBA好像是没有irq这种线,你说的控制信号sel,enable难道不算?

ack的信号据我的理解应该要不就是你的rdata或者是irq,fiq这种线接过去cpu才能知道的(轮询or中断)

?

其实比较纠结的是从机的反馈信号。AHB上面的从机可以通过HREADY和HRESP[1:0]反馈当前状态给CPU。但是APB上面的从机就没有提供这种反馈信号线。你说的sel、enable确实是控制信号,但它们是受主机控制断言/取消。APB从机的反馈信号看来只能单独送给CPU了。

apb又不是直接连给cpu的 信号想怎么给就怎么给

你的bridge里搞个对hready和hresp的逻辑不就一样用了

嗯,你说的对。很高兴和你讨论,感谢!