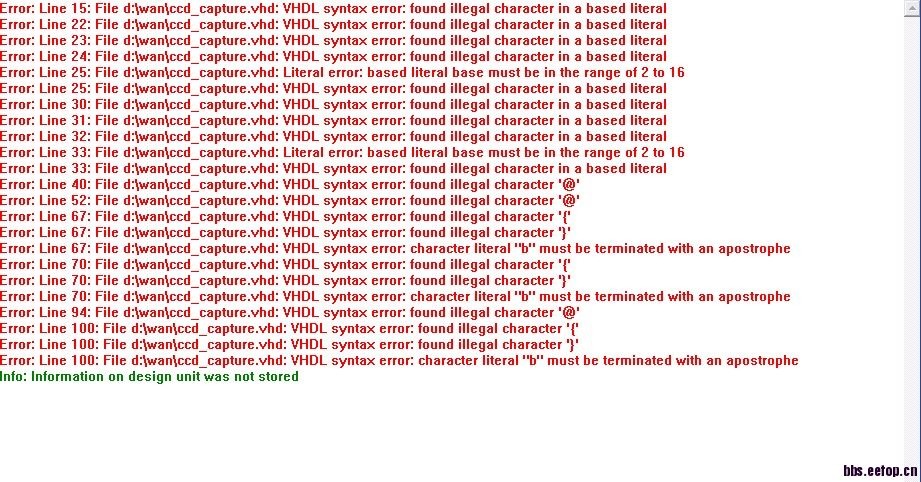

利用verilog 实现CCD的控制 这程序编译时有32个错误 请高手矫正

1 module CCD_Capture (

2 oDATA,

3 oDVAL,

4 oX_Cont,

5 oY_Cont,

6 oFrame_Cont,

7 iDATA,

8 iFVAL,

9 iLVAL,

10 iSTART,

11 iEND,

12 iCLK,

13 iRST

14 );

15

16 input [9:0] iDATA;

17 input iFVAL;

18 input iLVAL;

19 input iSTART;

20 input iEND;

21 input iCLK;

22 input iRST;

23 output [9:0] oDATA;

24 output [10:0] oX_Cont;

25 output [10:0] oY_Cont;

26 output [31:0] oFrame_Cont;

27 output oDVAL;

28 reg Pre_FVAL;

29 reg mCCD_FVAL;

30 reg mCCD_LVAL;

31 reg [9:0] mCCD_DATA;

32 reg [10:0] X_Cont;

33 reg [10:0] Y_Cont;

34 reg [31:0] Frame_Cont;

35 reg mSTART;

36

37 assign oX_Cont = X_Cont;

38 assign oY_Cont = Y_Cont;

39 assign oFrame_Cont = Frame_Cont;

40 assign oDATA = mCCD_DATA;

41 assign oDVAL = mCCD_FVAL&mCCD_LVAL;

42

43 always@(posedge iCLK or negedge iRST)

44 begin

45

if (!iRST)

46 mSTART <= 0;

47

else

48 begin

49

if (iSTART)

50 mSTART <= 1;

51

52

if (iEND)

53 mSTART <= 0;

54 end

55 end

56

57 always@(posedge iCLK or negedge iRST)

58 begin

59

if (!iRST)

60 begin

61 Pre_FVAL <= 0;

62 mCCD_FVAL <= 0;

63 mCCD_LVAL <= 0;

64 mCCD_DATA <= 0;

65 X_Cont <= 0;

66 Y_Cont <= 0;

67 end

68

else

69 begin

70 Pre_FVAL <= iFVAL;

71

if (({Pre_FVAL,iFVAL}==2'b01) && mSTART)

72 mCCD_FVAL <= 1;

73

else

if ({Pre_FVAL,iFVAL}==2'b10)

74 mCCD_FVAL <= 0;

75

76 mCCD_LVAL <= iLVAL;

77 mCCD_DATA <= iDATA;

78

79

if (mCCD_FVAL)

80 begin

81

if (mCCD_LVAL)

82 begin

83

if (X_Cont<1279)

84 X_Cont <= X_Cont + 1;

85

else

86 begin

87 X_Cont <= 0;

88 Y_Cont <= Y_Cont + 1;

89 end

90 end

91 end

92

else

93 begin

94 X_Cont <= 0;

95 Y_Cont <= 0;

96 end

97 end

98 end

99

100 always@(posedge iCLK or negedge iRST)

101 begin

102

if (!iRST)

103 Frame_Cont <= 0;

104

else

105 begin

106

if (({Pre_FVAL,iFVAL}==2'b01) && mSTART)

107 Frame_Cont <= Frame_Cont+1;

108 end

109 end

110

111 endmodule 希望得到高人的指点

错误有报告 你要是看不懂就不要看了

可以回家种地了

很多人都用C的思想写verilog,当然很多错误了。

verilog虽然语法像C,但根本就不是一回事。

32个错误在哪里呢?怎么不把报错贴出来?

而且,贴上来的代码很乱,很难阅读。哎。哪里有那么好的人,一行行的帮你检查代码啊。一点点提示都没有。

编译了一下 好像没有问题啊 ncvlog 编译无错误

我只是去掉了行号和空行

作者太强大了

谢谢您的提醒 这个是我编译时提示的错误 很希望得到大家的帮助

您好 我看着程序感觉也没有太大的问题 但是@ 这种符号都提示是非法的 我不知道是为什么 软件我用的是 max+plus 如果您知道为什么 可以回答一下吗 最好您可以把仿真图传上来,具体的时序我也不知道对不对 非常感谢!

是的 我也是从C51直接学的FPGA 真心难改啊

这是Verilog语言写的代码,而你保存成.vhd后缀名,软件就当是VHDL来编译,自然就报错了。

改成.v后缀再重新添加吧

楼上是正解。

学习了

非常好的讨论

对 别搞成vhdl的

您好 真的是这样的 我网上看的教程是错的 谢谢您的指教 !谢谢楼上的各位。

嘿嘿 新手再次感谢大家的热心指导 !